DAPU TELECOM

## DPSync SONET/SDH/SyncE/PTP synchronization platform ACS9522

FINAL

# ABOUT THE ACS9522

This is the datasheet for the DPSync ASSP ACS9522 variant. The datasheet should be read in conjunction with the ACS9522 user guide, API documentation and other information available at the DPSync Resource Center<sup>1</sup>. There are many applications in which it is necessary to lock a remote clock signal to a central frequency source, and there are other applications which require the alignment of a clock to a central source of time. The ACS9522 combines DAPU's synchronous equipment timing source (SETS) functionality and DPSync packet timing technology and can therefore be used for both applications.

In this datasheet, the words SETS and TDM Block are synonymous, and both terms are used.

SETS functionality is used for frequency-locking applications in SDH/SONET and Ethernet equipment. DPSync technology combines the IEEE 1588 v2 protocol with DAPU's patented packet delay filtering algorithms, which allow a reference clock to be transported across a packet switched network without special adaptations of switches or routers in the network. It is ideal for carrying timing across a legacy packet switched network. IEEE 1588 is often known as precision time protocol (PTP), the acronym that is generally used in this document. The ACS9522 supports:

Timebase derived from:

PTP slave, SONET/SDH recovered clock, BITS/SSU input, SyncE recovered clock, GPS, 1PPS, precision holdover. Physical layer clock sources are jitter and wander attenuated according to G.812, G.813, G.8261, G.8262, GR-1244-CORE, GR253 etc.

Technology bridging:

Derive timing from one input technology (SONET, SDH, SyncE, PTP) and provide timing to all output technologies simultaneously.

PTP Grandmaster:

PTP Grandmaster function supports multiple PTP slaves using multicast or unicast messaging. Timebase may be PTP or ARB.

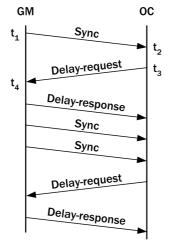

### PTP Slave:

Acting as a PTP Ordinary Clock in Slave mode, the ACS9522 can lock to BCs or TCs, or it can use sophisticated packet delay filters and adaptation algorithms to lock to a remote PTP Grandmaster over a multi-hop legacy network which has no PTP support. TDM/clocks:

Includes all DAPU SETS family functions for physical layer input and output synchronization.

SyncE:

Integrates DAPU eSETS technology for the physical layer input and output synchronization of Ethernet PHY devices. Self test - the device self-checks for consistency and makes rudimentary checks of the external Ethernet PHYs.

# FEATURES

## **PTP** timing features

- PTP Grandmaster selection automatic or manual PTP master/slave mode selection.

- Powerful network delay analysis full time-alignment in the slave over hostile networks (Layer 2 or Layer 3 networks).

- Dynamic adaptation to network delay variations. Network loading change tolerant (e.g., ramps and steps).

- Time alignment better than ±1 µs on a managed 10-switch GbE network under G.8261<sup>20</sup> test conditions.\*

- Frequency alignment better than ±10 ppb on a managed 10-switch GbE network under G.8261<sup>20</sup> test conditions.\*

### **TDM** timing features

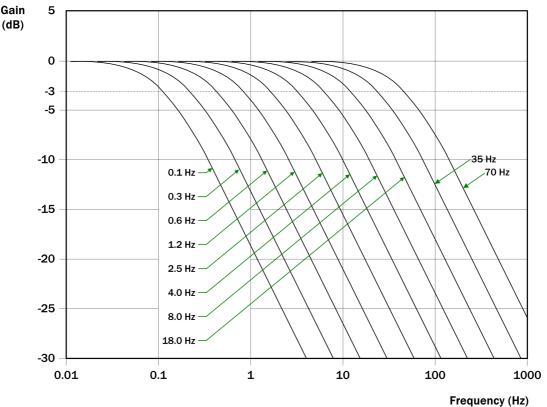

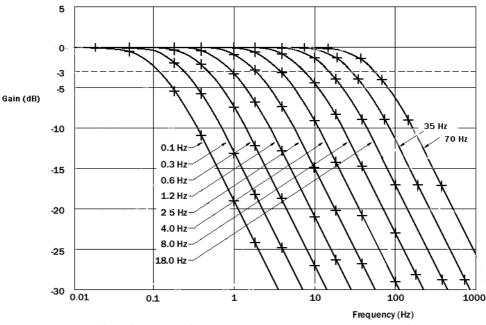

- Programmable TDM timing bandwidth for wander and jitter tracking/attenuation, 0.1 Hz to 70 Hz in 10 steps.

- Automatic hit-less source switchover on loss of input.

- Output clock phase adjustment in 6 ps steps to ±200 ns.

Device features

- Fully integrated integrates hardware precision timestamping with on-the-fly insertion. Powerful integrated processor and clock recovery algorithm for PTP.

- Timing synchronization on a chip supporting transitions from legacy circuit networks to new packet technology.

- Suitable applications Stratum 3, 3E, 4E, 4, SONET Minimum Clock (SMC) or SONET/SDH Equipment Clock (SEC) or Ethernet, IEEE1588<sup>13</sup> PTP, Synchronous Ethernet, Ethernet Equipment Clock.

- Clocks 18 clock inputs and 11 clock outputs.

- Precision holdover in all modes.

- Ports 2 x SGMII, serial interface and JTAG.

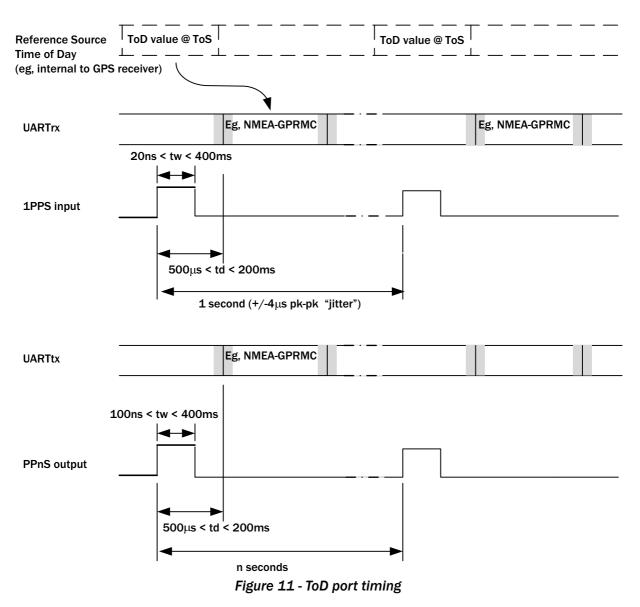

- Time-of-day PPnS top-of-second signal plus current-time-since-epoch message on a UART.

- Output characteristics:

. Time-aligned output pair: 1 PPS and 125 MHz divided by n (n = 4 to 125000). Frequency-aligned outputs:

1 Hz and programmable frequency 1 kHz to 62.5 MHz. *Low jitter frequency-aligned outputs:*

- SONET and SDH OC-n rates: 3.84 MHz to 155.52 MHz. SyncE rates: 25 MHz, 50 MHz, 62.5 MHz and 125 MHz.

- Local oscillator: ±20 ppm or better.

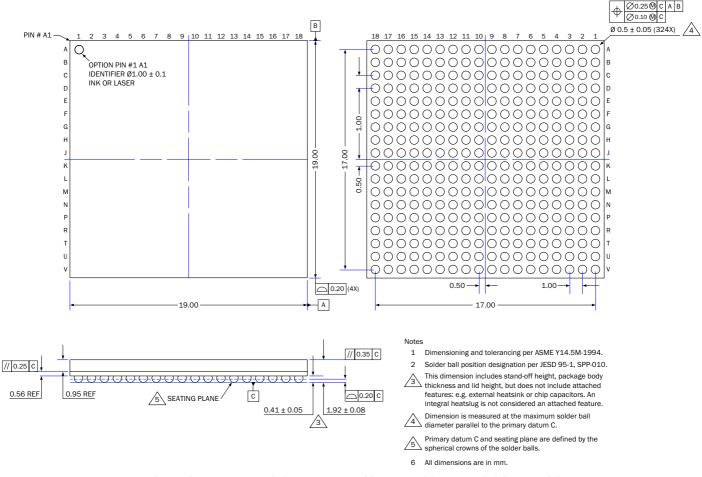

- LBGA package: 324 pin, 19 mm x 19 mm. Lead-free - RoHS<sup>26</sup> and WEEE<sup>27</sup> compliant.

- External RAM not required.

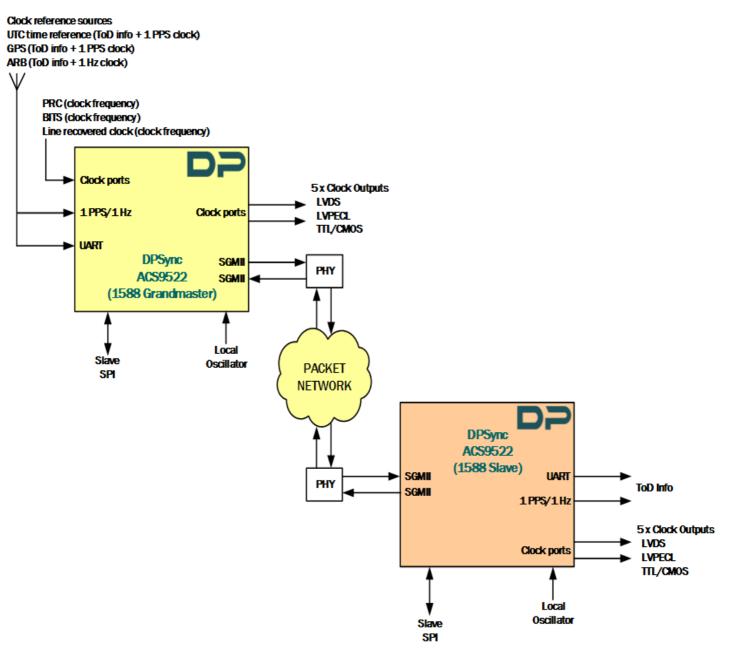

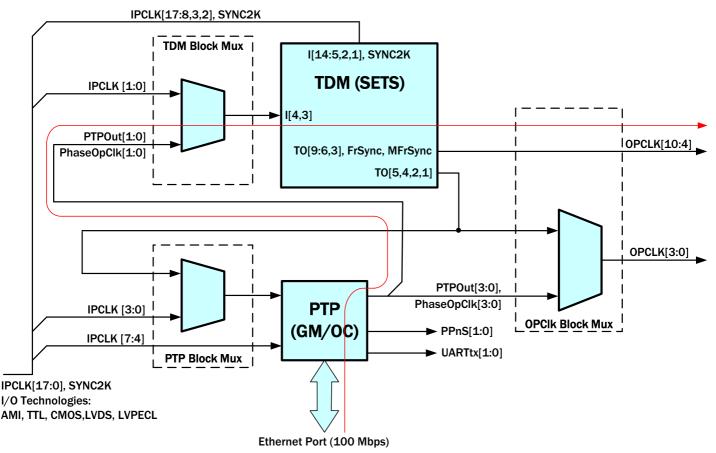

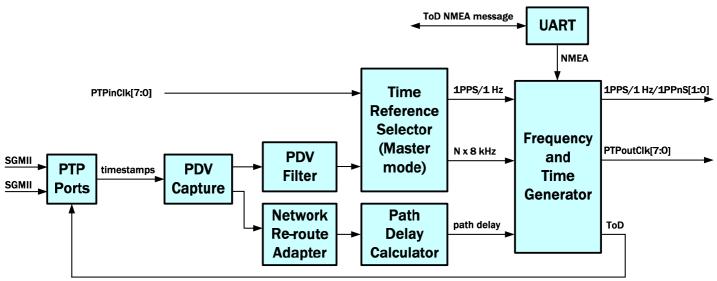

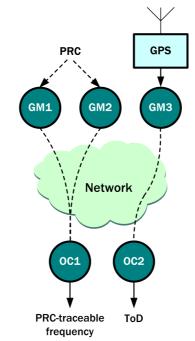

A simplified system diagram is shown in Figure 1.

\* This is an indication of DAPU tested performance and is not guaranteed across all types of switches and network conditions. Please contact DAPU DPSync support for further details.

ACS9522

**FINAL**

# System diagram

Figure 1 - Simplified system diagram - ACS9522 DPSync in PTP Grandmaster and Slave modes

| Section                                                | Page       |

|--------------------------------------------------------|------------|

| ABOUT THE ACS9522                                      | 1          |

| FEATURES                                               | 1          |

| System diagram                                         | 2          |

| OVERVIEW                                               | 7          |

| Physical layer timing                                  | 7          |

| Interaction of TDM and PTP blocks                      |            |

| Clock generation in a combined PTP/TDM application     |            |

| Enhancement of PTP Grandmaster clock                   |            |

| Enhancement of ordinary clock                          |            |

| Enhancement of the TDM Block                           | 11         |

| PIN DIAGRAMS                                           | 12         |

| ACS9522                                                |            |

| Pin descriptions                                       | 14         |

|                                                        |            |

| Interfaces                                             |            |

| Input reference clocks                                 |            |

| AMI input and output ports                             |            |

| LVPECL input and output ports                          |            |

| LVDS input and output ports<br>Time of day port        |            |

| Jitter tolerance of the 1PPS input                     |            |

| Time of day message format                             |            |

| GPRMC message format                                   |            |

| Phase aligned output clock port                        |            |

| Serial peripheral interface                            |            |

| SGMII interfaces                                       |            |

| I2C interface                                          | <b>3</b> 6 |

| JTAG port                                              |            |

| Operating mode selection port                          |            |

| Local oscillator clock                                 |            |

| Oscillator frequency selection                         |            |

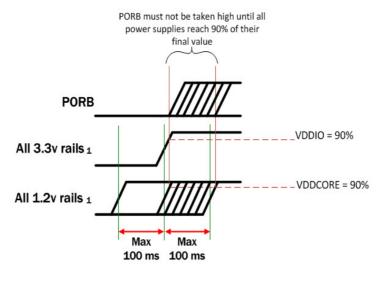

| Reset (PORB)                                           |            |

| Locked status<br>Firmware specific input/output (IO)   |            |

| Power supply and internally connected pins and grounds |            |

| Power supply and grounds                               |            |

| Internally connected pins                              |            |

| ELECTRICAL SPECIFICATIONS                              |            |

| Electrical protection                                  | 30         |

| Over-voltage protection                                |            |

| ESD protection                                         |            |

| Latchup protection                                     |            |

| Absolute maximum ratings                               |            |

| Operating conditions                                   | <b>4</b> 1 |

| DC characteristics                                     | <b>4</b> 2 |

| DESCRIPTION OF BLOCK DIAGRAM                           |            |

| The PTP Block                                          |            |

| PTP port                                               |            |

# DPSync ACS9522

# FINAL

| Section                                                          | Page       |

|------------------------------------------------------------------|------------|

| PTP port API calls                                               | <b>4</b> 4 |

| PDV capture                                                      |            |

| PDV filter                                                       |            |

| Network re-route adapter                                         |            |

| Path delay calculator                                            |            |

| PTP input reference port (time selector)                         |            |

| UART                                                             |            |

| Frequency and time generator                                     |            |

| Phase-aligned clock port                                         |            |

| Importance of the local oscillator                               |            |

| Self test                                                        |            |

| The TDM Block                                                    |            |

| SETS reference sources                                           |            |

|                                                                  |            |

| Monitors                                                         |            |

| TO source selection                                              |            |

| T4 source selection                                              |            |

| TO digital phase-locked loop                                     |            |

| T4 digital phase-locked loop                                     |            |

| T4 output selection                                              |            |

| TO analog phase-locked loop, clock dividers and output selectors |            |

| T4 analog phase-locked loop, clock dividers and output selectors |            |

| SETS output selection                                            |            |

| USING THE TDM BLOCK                                              | <b>5</b> 0 |

| INPUT REFERENCE CLOCK PORTS IN THE TDM TIMING MODE               | 51         |

| LOCKING MODES                                                    | <b>F</b> 1 |

|                                                                  |            |

| Direct lock mode                                                 |            |

| Lock8K mode                                                      |            |

| DivN mode                                                        |            |

| DivN Examples                                                    |            |

| LVPECL and/or LVDS input port selection                          |            |

| AMI input port selection                                         |            |

| Clock quality monitoring in the TDM Block                        |            |

| Activity monitoring in TDM Timing mode                           |            |

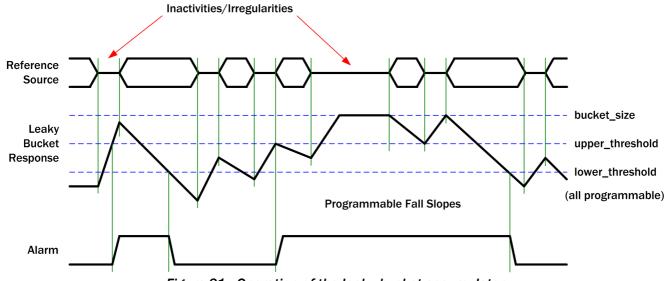

| Leaky bucket timing                                              |            |

| Frequency monitoring of clock inputs                             |            |

| Selection of input reference clock sources                       |            |

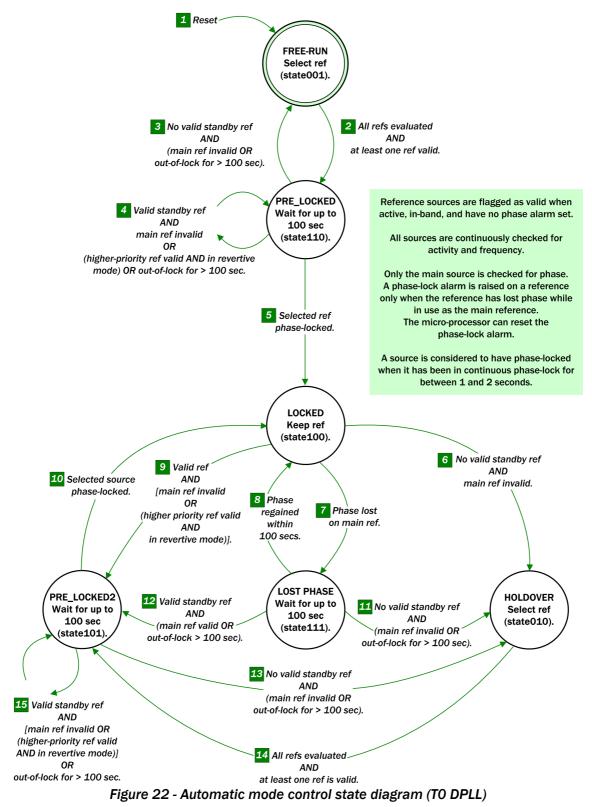

| Automatic selection control                                      |            |

| Ultra fast switching                                             |            |

| Output clock phase continuity on source switchover               |            |

| Modes of operation                                               |            |

| Free-run mode                                                    |            |

| Pre-locked mode                                                  |            |

| Locked mode                                                      |            |

| Lost-phase mode                                                  |            |

| Holdover mode                                                    |            |

| Automatic holdover mode                                          |            |

| Manual holdover mode                                             |            |

| Mini-holdover mode                                               |            |

| External factors affecting holdover mode                         |            |

| Pre-locked2 mode                                                 |            |

| DPLL architecture and configuration                              |            |

| TO DPLL main features                                            | 61         |

| Section                                                                                         | Page       |

|-------------------------------------------------------------------------------------------------|------------|

| T4 DPLL main features                                                                           |            |

| TO DPLL automatic bandwidth controls                                                            | <b>6</b> 2 |

| Phase and frequency detectors                                                                   |            |

| Phase lock/loss detection                                                                       |            |

| Damping factor programmability                                                                  |            |

| Local oscillator frequency calibration                                                          |            |

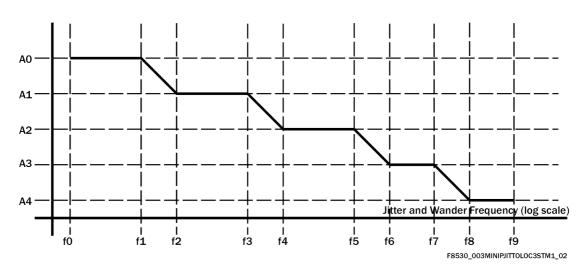

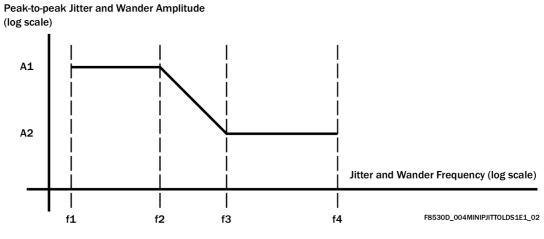

| Output jitter and wander                                                                        |            |

| Jitter and wander transfer                                                                      |            |

| Phase build-out                                                                                 |            |

| PBO phase offset                                                                                |            |

| Input to output phase adjustment                                                                |            |

| Input wander and jitter tolerance<br>Using the DPLLs for accurate frequency and phase reporting |            |

| Frequency reporting                                                                             |            |

| Phase reporting                                                                                 |            |

| Output clock paths                                                                              |            |

| LVPECL/LVDS/AMI output port selection                                                           |            |

| Output frequency selection and configuration                                                    |            |

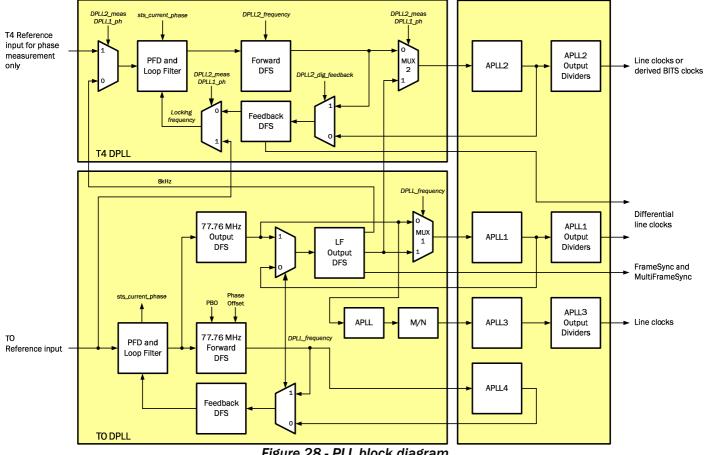

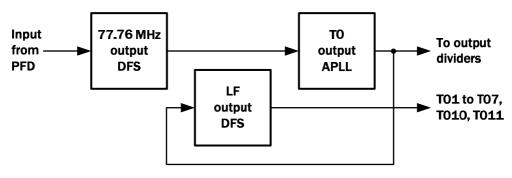

| TO DPLL and APLLs                                                                               |            |

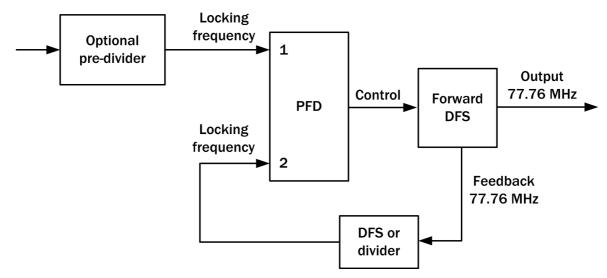

| TO input frequency, locking frequency and feedback frequency                                    |            |

| TO digital versus analog feedback                                                               |            |

| TO PBO and phase offset                                                                         | <b>7</b> 2 |

| TO output DFS blocks                                                                            |            |

| TO output APLL and output dividers                                                              |            |

| T4 DPLLs and APLLs                                                                              |            |

| T4 forward DFS and feedback DFS                                                                 |            |

| T4 output APLL and dividers                                                                     |            |

| Additional outputs                                                                              |            |

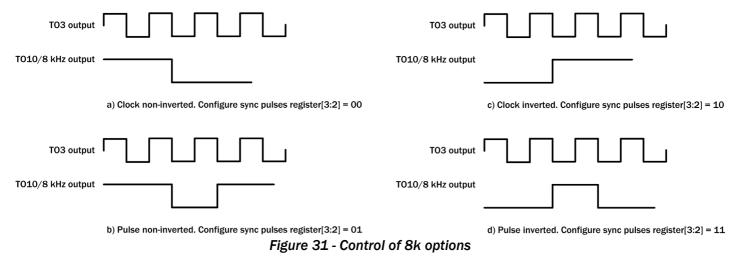

| 2 kHz and 8 kHz clock outputs                                                                   |            |

| Steps to configure the output frequencies<br>Jitter performance                                 |            |

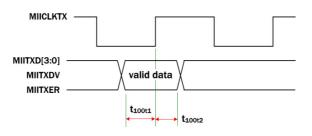

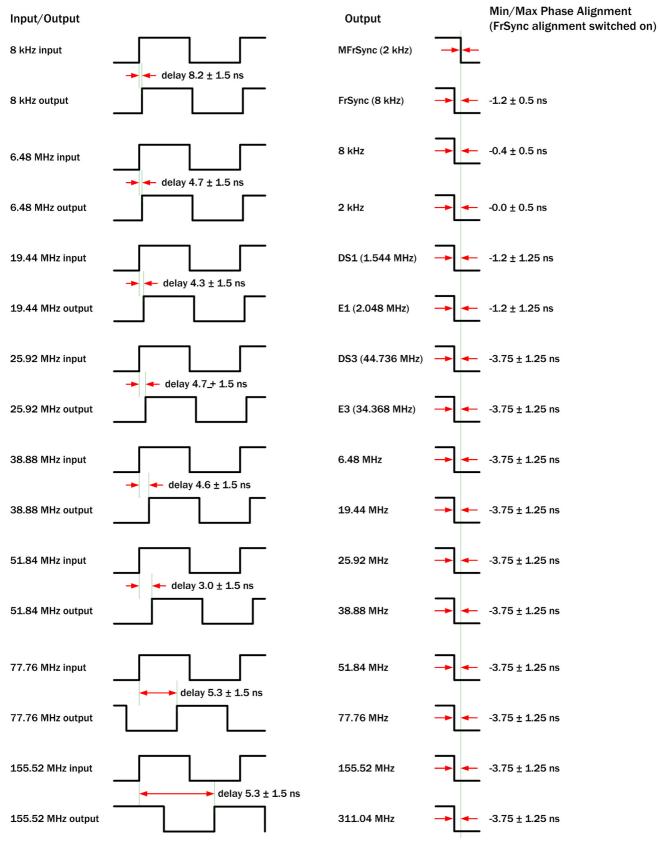

| Input/output timing                                                                             |            |

| T4 low frequency outputs                                                                        |            |

| Jitter on the low frequency outputs                                                             |            |

| Digital1 and Digital2 outputs                                                                   |            |

| Jitter on the Digital1 and Digital2 outputs                                                     |            |

| Interrupt requests from the TDM Block                                                           |            |

| CONTROL REGISTERS OF THE TDM BLOCK                                                              |            |

| TDM Block register organisation                                                                 | 83         |

| Multi-word registers                                                                            |            |

| Register access                                                                                 |            |

| Configuration registers                                                                         |            |

| Status registers                                                                                |            |

| Default values                                                                                  | <b>8</b> 3 |

| TDM Block register map                                                                          | <b>8</b> 4 |

| TDM Block register descriptions                                                                 |            |

| APPLICATIONS                                                                                    | <b></b>    |

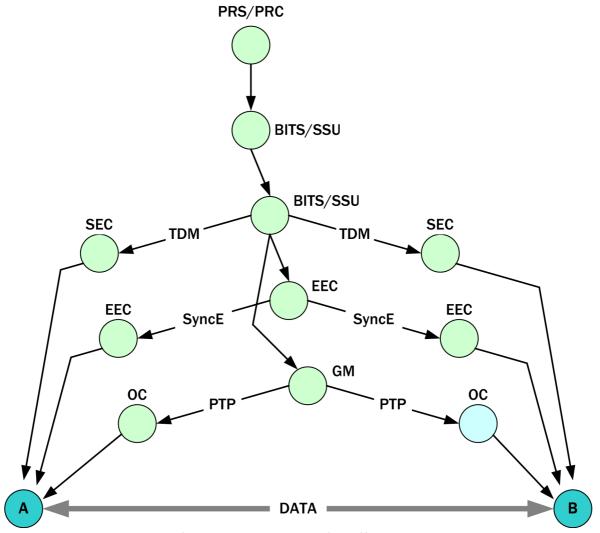

| Next-generation timing                                                                          |            |

| PTP messages<br>Grandmaster selection (default IEEE 1588 BMCA)                                  |            |

| BMCA selection based on priority                                                                |            |

| Section                                                                            | Page        |

|------------------------------------------------------------------------------------|-------------|

| BMCA selection based on reference quality<br>BMCA in Multicast vs Unicast networks |             |

| Acceptable Master Table                                                            |             |

| Reference sources for telecom applications                                         |             |

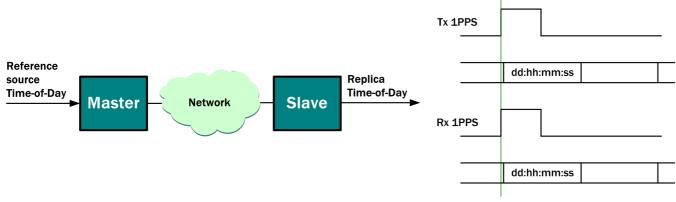

| ToD applications                                                                   |             |

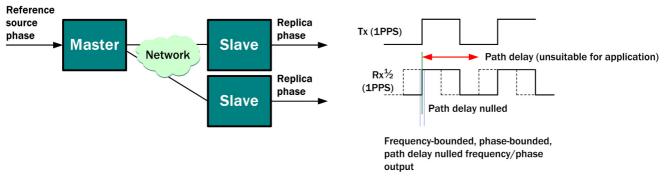

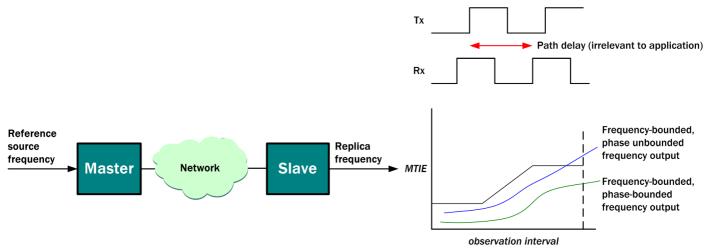

| Common-phase applications<br>Frequency-transfer applications                       |             |

| Sources of error in PTP networks                                                   |             |

| Influences on Grandmaster fan-out                                                  |             |

| TDM timing                                                                         | <b>19</b> 4 |

| PACKAGE DETAILS                                                                    |             |

| Thermal conditions                                                                 |             |

| GENERAL INFORMATION                                                                |             |

| Acronyms and abbreviations                                                         |             |

| References and related standards                                                   | <b>20</b> 1 |

| Trademark acknowledgements                                                         | <b>20</b> 3 |

| Product status/datasheet revision history                                          | <b>20</b> 3 |

| Product status                                                                     |             |

| Datasheet revision                                                                 | <b>20</b> 3 |

| Ordering information                                                               | <b>20</b> 4 |

| Disclaimers                                                                        | <b>20</b> 4 |

# **OVERVIEW**

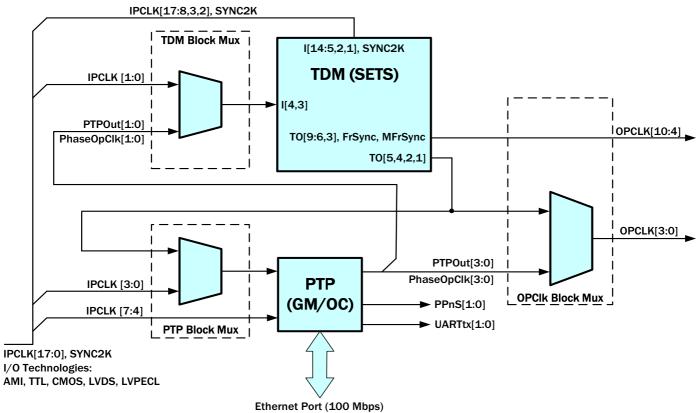

Figure 2 is a block diagram of the ACS9522 device, showing that it contains both TDM and PTP blocks. These blocks can be used separately or in conjunction with each other to provide a highly-flexible, multi-role device that can provide clock timing in traditional TDM equipment, or packet-timing in next-generation packet switching equipment. For packet-timing, the device supports packet-based timing transfer using Precision Time Protocol, and physical-layer-based timing transfer using Synchronous Ethernet.

Figure 2 - Overall block diagram of the ACS9522

# **Physical layer timing**

The TDM Block can be used to provide a dedicated SETS function independent of PTP operation. In SDH/SONET equipment, the TDM Block can produce the SEC: in Synchronous Ethernet equipment, it can produce the EEC.

The TDM Block is controlled using direct accesses to the control and status registers (see TDM Block register map).

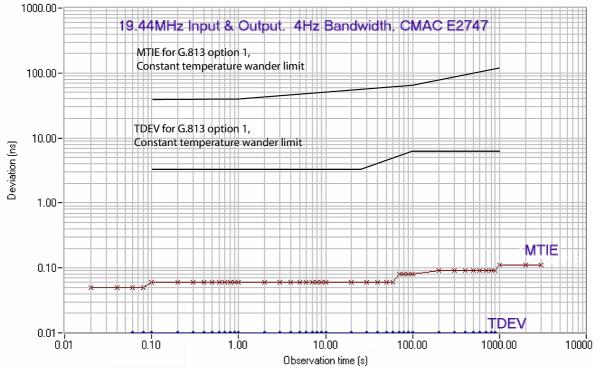

The TDM Block may be hardwired to the IPCLK input and OPCLK output pins via the TDM Block Multiplexer and the OPCLK Block Multiplexer. Performance of noise-transfer, phase-transient-generation, holdover etc. is well within standardized requirements. See Figure 20 for sample wander and jitter transfer functions.

# Interaction of TDM and PTP blocks

## Clock generation in a combined PTP/TDM application

The TDM and PTP blocks are independent units that discretely provide appropriate functionality for their basic roles. Indeed, the TDM Block provides full SETS functionality with no assistance from the PTP Block, and the PTP Block provides PTP Grandmaster Clock and Slave Clock functionality without help from the TDM Block. However, by making the blocks work together, the range of applications is expanded and performance can be enhanced.

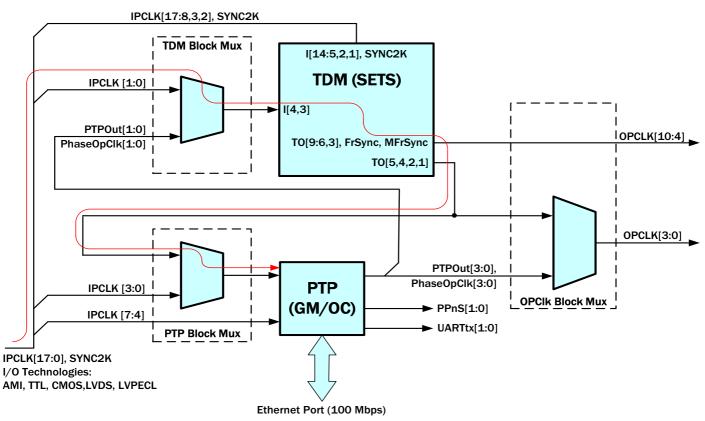

This section describes how to make the TDM Block and the PTP Block interact to enhance the basic performance of PTP Grandmaster, PTP Slave and SETS functions. The configuration involves the use of the TDM Block Multiplexer, the PTP Block Multiplexer and the OPCLK Block Multiplexer, which interconnect the TDM and PTP blocks. The multiplexers are controlled by dedicated API calls (see the ACS9522 Application Note <sup>32</sup>).

An ACS9522 can support both PTP and traditional TDM applications at the same time, either as a GM clock or as an OC. As a GM, an ACS9522 is capable of simultaneously generating PTP packets as well as output clocks, irrespective of the type of reference signal supplied to it. The output clocks may be referenced to the same reference source as the PTP packets or to some other reference source. For example, the device may generate PTP packets and TO TDM clocks referenced to one reference source, whilst it also generates a T4 output clock referenced to another reference source. For a definition of the T0 and T4 clock signals, please refer to ITU-T Recommendation G.783<sup>11</sup>.

The capability to generate multiple output clocks from separate references also embraces situations when the ACS9522 acts as an OC (where the TO clock would be referenced to the PTP GM reference), and it allows the device to be used as a comprehensive timing device to suit a multitude of applications.

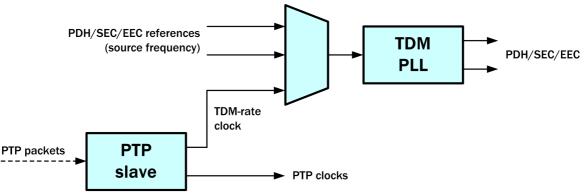

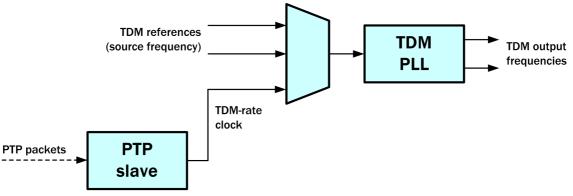

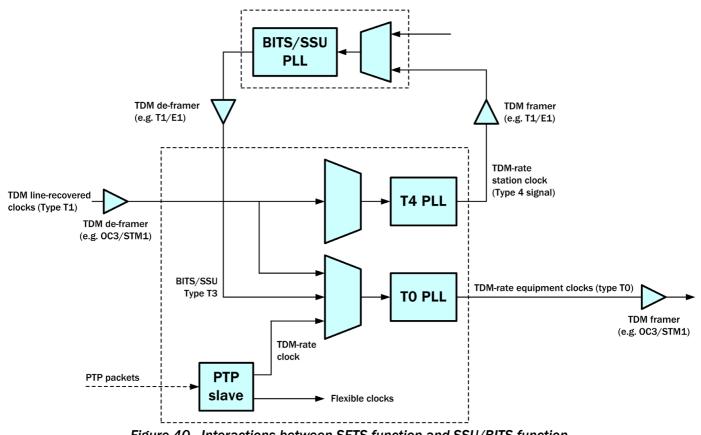

Figure 3 shows an example of a PTP-recovered clock being added to the possible references from which a SETS function may select a source.

Figure 3 - PTP Block enhancing TDM Block

## **Enhancement of PTP Grandmaster clock**

The PTP Block can accept up to 8 wired clocks. These can come from the first 8 of the 18 possible IPCLK clocks: 4 of the 8 clocks can also be routed from the TDM module. One of the 8 clock inputs can be selected as a reference for the PTP block (see ACS9522 Application Note <sup>32</sup>).

Using the TDM Block to enhance the PTP Block increases the range of clock signal frequencies that can be supported, improves the monitoring, and adds noise-reduction on the selected reference, along with phase build-out on switches between clock references. Conversely, without the use of the TDM Block, the PTP Block requires quieter clocks to achieve the same timebase stability. The PTP Block also has limited activity monitoring and no phase build-out capabilities, so it expects references to be phase-aligned. For 1PPS signals this is a reasonable expectation, but not for line-recovered clocks or even BITS clocks. So using the TDM Block to add the features described above is worthwhile.

The TDM Block can be brought into play by routing the input references to it via the TDM Block Multiplexer and setting up the TDM Block to suit the requirements. The output of the TDM Block can then be routed to the PTP Block, via the PTP Block Multiplexer, to act as a reference frequency source. If more than one reference source is available to the TDM Block, then the TDM Block can be configured to use them in a predefined order. It will apply phase build-out when necessary to maintain a tight output phase. It will apply the noise filter, with the selected bandwidth, and will generate the selected output frequency on the selected output.

This output signal should then be routed into the PTP Block by selecting the appropriate bit of the PTP Block Multiplexer and setting it to route the signal through. An example configuration is shown in Figure 4, although many other configurations are possible.

Figure 4 - Example of GM configuration for frequency transfer via PTP

The PTP Block can be supplied with references directly, without going through the TDM Block first. This would be the case when a reference supplies ToD, when the signal fed to the PTP Block would be a 1PPS signal, but other frequencies could be supplied also. These signals must not have significant levels of jitter or wander or they will disturb the stability of the GM timebase.

## Enhancement of ordinary clock

All output signals of the PTP Block are driven by digital circuitry. Clock outputs change state on the nearest edge of a highfrequency internal oscillator. These edges rarely occur at exactly the right time for the output clock and so all output clocks which are generated by the PTP Block will contain jitter. For low-frequency output clocks, this jitter will be a small fraction of the unit interval and so should be suitable for direct use without needing additional jitter reduction measures. Higher-frequency signals may not meet the jitter requirements directly and may need additional jitter reduction measures.

When the output clock operates at a frequency used by telecom networks, the TDM Block may be able to perform this jitter reduction since it contains analog phase locked loops designed for low jitter at frequencies up to 155.52 MHz. If required, the TDM Block can be used to so enhance the PTP Block by routing the output signal(s) of the PTP Block to the TDM Block input(s) using the TDM Block Multiplexer (see ACS9522 Application Note <sup>32</sup>).

In addition to reducing jitter, the TDM Block can adapt the frequency of the clock signal if required. The TDM Block also provides a pair of differential outputs (LVPECL or LVDS) which can be used for frequencies up to 155.52 MHz. Figure 5 shows an example configuration.

Figure 5 - TDM Block enhancing the PTP Block

## Enhancement of the TDM Block

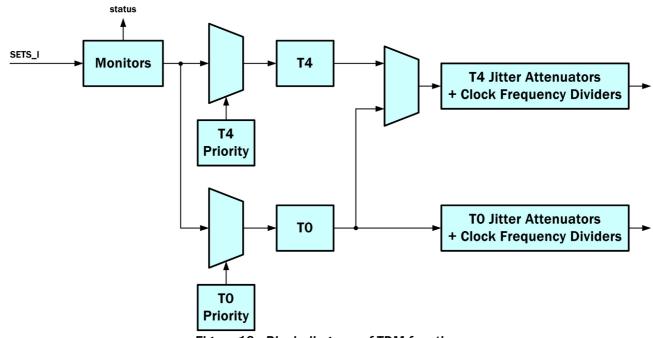

The TDM Block provides SETS functionality for use in traditional TDM applications. But by using the PTP Block as well, the functionality is enhanced by adding a PTP OC. Figure 6 shows an example in which the SETS function of the TDM Block is supplied conventionally with a number of BITS and/or line clocks and, in addition, is supplied with a clock recovered by the PTP Block (acting as an OC). The PTP-recovered clock must be operating at a frequency acceptable to the TDM Block (for example n x 8 kHz).

Figure 6 - PTP Block enhancing the TDM Block

All of the clocks supplied to the TDM Block are routed through the TDM Block Multiplexer. The TDM Block can select any of the supplied clocks as the reference source for the TO channel, in accordance with a priority held in either the SETS TO priority table or host software. The TDM Block can also select an input for the T4 channel if that is required. The input will be selected according to a priority held in either the SETS T4 priority table or host software.

The final output clock is produced by the TDM Block.

The TDM Block can also perform the new EEC function required by ITU Recommendation G.8262<sup>29</sup> for Synchronous Ethernet applications.

# **PIN DIAGRAMS**

## ACS9522

Figure 7 shows the pinout arrangement of the ACS9522. Click on a pad for more detailed information. Pins of the same colour in Figure 7 may be grouped into buses in the Boundary Scan Description Language (BSDL) file.

|   | 18             | 17        | 16       | 15       | 14       | 13       | 12       | 11           | 10             | 9       | 8               | 7        | 6       | 5                | 4             | 3             | 2                 | 1             |

|---|----------------|-----------|----------|----------|----------|----------|----------|--------------|----------------|---------|-----------------|----------|---------|------------------|---------------|---------------|-------------------|---------------|

| A | VSS            | IC 04     | NC       | NC       | NC       | IC 03    | NC       | NC           | NC             | NC      | NC              | NC       | NC      | IC 02            | IC 01         | VSS           | VSS               | VSS           |

| В | VSS            | VDDIO     | VDDIO    | VDDIO    | VDDIO    | VDDIO    | VDDIO    | NC           | NC             | NC      | NC              | NC       | VSS     | VSS              | VSS           | VSS           | VDDIO             | VSS           |

| с | VSS            | VSS       | VSS      | VSS      | VSS      | VSS      | VDDIO    | IC 05        | REFCLK         | NC      | NC              | NC       | VSS     | VSS              | VSS           | VSS           | VDDIO             | SGMIICLK<br>P |

| D | VDDIO          | VSS       | VSS      | VSS      | VSS      | VSS      | VDDIO    | IPCLK1       | IPCLK5s        | IPCLK7  | IC 06           | NC       | VSS     | VSS              | VSS           | VSS           | VDDIO             | SGMIICLK<br>N |

| Е | VDDIO          | VSS       | VSS      | VSS      | VSS      | VSS      | VDDIO    | IPCLKO       | IPCLK2         | IPCLK3  | IC 09           | OPCLK1   | VSS     | VSS              | VSS           | IC 08         | IC 07             | SGMIICLK      |

| F | VDDIO          | VSS       | VSS      | VSS      | VSS      | VSS      | VDDIO    | IPCLK6       | IPCLK4         | LOCKED  | SGMIICLK<br>SEL | PPNS1    | VDDIO   | VDDIO            | IC 11         | NC            | IC 10             | VSS           |

| G | SYNC2K         | IPCLK16   | IPCLK15  | VDDIO    | VDDIO    | IC 15    | VDDIO    | SYSMODE<br>0 | IC 14          | IC 13   | SYSMODE<br>1    | PWMO     | VDDIO   | VDDIO            | VDDIO         | IC 12         | VDDASGMI<br>ITX1  | VSS           |

| Н | IPCLK11P<br>OS | IPCLK13   | IPCLK14  | IC 20    | IC 19    | IC 18    | OPCLK7   | VDDIO        | PORB           | ALARM   | SLVINT          | TRST     | VDDIO   | VDDIO            | IC 17         | IC 16         | VDDHASG<br>MIITX1 | TX1POS        |

| J | IPCLK11N<br>EG | IPCLK12   | IPCLK17  | IC 22    | VDDIO    | IC 21    | TDI      | VSS          | VSS            | SLVCSB  | VDDCORE         | OSCFSEL1 | VDDCORE | VDDCORE          | VDDCORE       | VSSSGMII<br>1 | VDDHASG<br>MIIRX1 | TX1NEG        |

| к | IPCLK8NE<br>G  | VDD_SETS  | VDD_SETS | VDD_SETS | VDD_SETS | IC 23    | SCL      | VDDIO        | VDDIO          | SLVMISO | SDA             | VDDIO    | VDDIO   | VDDIO            | VSSSGMII<br>1 | VDDSGMII<br>1 | VDDASGMI<br>IRX1  | RX1POS        |

| L | IPCLK8P0<br>S  | OPCLK10   | VSS      | VSS      | VSS      | VSS      | VDD_SETS | VSS          | SLVCFGSPI      | VDDCORE | VSS             | VSS      | VSS     | VSS              | VSS           | VSSSGMII<br>0 | VDDASGMI<br>IRXO  | RX1NEG        |

| М | OPCLK5PO<br>S  | OPCLK9    | VDD_SETS | VSS      | VSS      | VSS      | OSCFSELO | VSS          | SLVCFGCL<br>KE | SLVSCLK | VSS             | VSS      | VSS     | VSS              | VSS           | VDDSGMII<br>0 | VDDHASG<br>MIIRXO | RXONEG        |

| N | OPCLK5NE<br>G  | IPCLK10   | VDD_SETS | VSS      | VSS      | VSS      | IC 25    | IC 24        | VDDIO          | VSS     | VSS             | VSS      | VSS     | VSS              | VSS           | VSSSGMII<br>0 | VDDHASG<br>MIITXO | RXOPOS        |

| Ρ | OPCLK4NE<br>G  | IPCLK9    | VDD_SETS | VSS      | VSS      | ESVA3    | OPCLK8   | PPNS0        | VDDIO          | IC 26   | VDDIO           | VDDCORE  | VDDIO   | VDDCORE          | VDDIO         | GNDCMU        | VDDASGMI<br>ITX0  | TXONEG        |

| R | OPCLK4PO<br>S  | IC 30     | VDD_SETS | VSS      | VSS      | ESGNDA   | IC 29    | OPCLKO       | PWM1           | IC 28   | IC 27           | VDDCORE  | MDC     | VDDCORE          | UARTRXO       | VDDIO         | UARTTX1           | TXOPOS        |

| Т | OPCLK6PO<br>S  | IC 37     | VSS      | VSS      | VSS      | VSS      | IC 36    | OPCLK2       | DACOUT         | IC 35   | SLVMOSI         | IC 34    | IC 33   | IC 32            | UARTRX1       | IC 31         | VDDCMUD           | VDDCMUD       |

| U | OPCLK6NE<br>G  | ESGNDA    | TDO      | IC 44    | ESVA1    | VDD_SETS | SONSDHB  | OPCLK3       | IC 43          | DACPOS  | IC 42           | IC 41    | IC 40   | IC 39            | VDDIO         | IC 38         | VDDCMU            | VDDCMU        |

| V | VSS            | ESVA2     | тск      | INTREQ   | TMS      | ESGNDA   | IC 51    | VDDIO        | DACNEG         | IC 50   | IC 49           | IC 48    | IC 47   | IC 46            | MDIO          | IC 45         | UARTTXO           | VSS           |

|   |                |           | JTAG     | Co       | ntrol/al | arms     |          | SGM          | 111            |         | ToI             | D        |         | l <sup>2</sup> C |               | Input         | clocks            |               |

|   | 0              | utput clo | ocks     |          |          | SPI      |          | Powe         | er             |         | Ground          | b        |         |                  | Intern        | ally con      | nected            |               |

|   | Not connected  |           |          |          |          |          |          |              |                |         |                 |          |         |                  |               |               |                   |               |

## Figure 7 - ACS9522 pin diagram

# **Pin descriptions**

This section contains tables of descriptions in which the details of every pin of the ACS9522 are declared.

In the pin description tables, the following acronyms appear in the  $\ensuremath{\mathsf{I/O}}$  column:

- I = input.

- O = output.

- I/O = bi-directional.

The following acronyms appear in the Signal Type column:

- P = power.

- G = ground.

$TTL^{U}$  = TTL input with internal pull-up resistor greater than 20 kΩ.

$TTL_{D}$  = TTL input with internal pull-down resistor greater than 20 kΩ.

NOTE: All pins are 5 V tolerant except where stated otherwise.

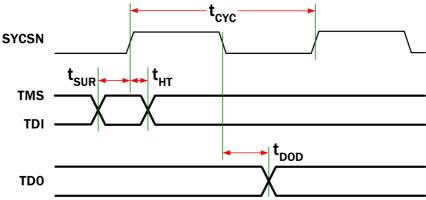

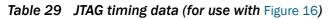

#### Table 1JTAG interface

| Pin | Symbol | I/0 | Signal type      | Description                                                                                                                                                                      |  |

|-----|--------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J12 | TDI    | I   | ττι <sup>υ</sup> | Boundary scan serial test data input<br>Sampled on rising edge of TCK.                                                                                                           |  |

| V14 | TMS    | I   | ττι <sup>υ</sup> | Boundary scan test mode select.<br>Sampled on rising edge of TCK.<br>If not used, connect to V <sub>DD</sub> or leave floating.                                                  |  |

| V16 | тск    | Ι   | TTL <sub>D</sub> | Boundary scan test clock input.                                                                                                                                                  |  |

| U16 | TDO    | 0   | ΤΤL <sup>U</sup> | Boundary scan serial test data output.<br>Sampled on rising edge of TCK.                                                                                                         |  |

| H7  | TRST   | I   | ΠL <sub>D</sub>  | Test reset input.<br>0 = boundary scan standby mode, allowing correct device operation.<br>1 = enable JTAG boundary scan mode.<br>If not used, connect to GND or leave floating. |  |

#### Table 2 Control and alarm pins

| Pin | Symbol   | I/0 | Signal type      | Description                                                                                               |  |

|-----|----------|-----|------------------|-----------------------------------------------------------------------------------------------------------|--|

| H10 | PORB     | I   | TTLU             | Power-on master reset (active-low).<br>0 = all internal states reset to default values.<br>1 = not reset. |  |

| F9  | LOCKED   | 0   | TTL/CMOS         | Device locked status pin:<br>0 = ACS9522 not in lock.<br>1 = ACS9522 in lock.                             |  |

| Н9  | ALARM    | 0   | TTL/CMOS         | Use subject to firmware version.<br>If not used, leave to float.                                          |  |

| J7  | OSCFSEL1 | I   | TTL <sub>D</sub> | Oscillator frequency select pins, which set the expected local oscillator frequency.                      |  |

| M12 | OSCFSELO | I   | TTL <sub>D</sub> | nequency.                                                                                                 |  |

| U12 | SONSDHB  | I   | TTL              | Selects between SONET and SDH signal rates:<br>0 = SDH.<br>1 = SONET.                                     |  |

| V15 | INTREQ   | 0   | TTL              | Interrupt request output.                                                                                 |  |

| G7  | PWMO     | 0   | TTL              |                                                                                                           |  |

| R10 | PWM1     | 0   | TTL              |                                                                                                           |  |

| T10 | DACOUT   | 0   | Analog           | Contact DAPU for application information.                                                                 |  |

| U9  | DACPOS   | I   | Analog           |                                                                                                           |  |

| V10 | DACNEG   | I   | Analog           |                                                                                                           |  |

### Table 3 SGMII Interface

| Pin | Symbol      | I/0 | Signal type                         | Description                                                                                             |

|-----|-------------|-----|-------------------------------------|---------------------------------------------------------------------------------------------------------|

| R1  | TXOPOS      | 0   | LVDS                                | SGMII Port 0, TX data output.                                                                           |

| P1  | TXONEG      |     |                                     |                                                                                                         |

| N1  | RXOPOS      | I   | LVDS                                | SGMII Port 0, RX data input.                                                                            |

| M1  | RXONEG      |     |                                     |                                                                                                         |

| H1  | TX1POS      | 0   | LVDS                                | SGMII Port 1, TX data output.                                                                           |

| J1  | TX1NEG      |     |                                     |                                                                                                         |

| K1  | RX1POS      | I   | LVDS                                | SGMII Port 1, RX data input.                                                                            |

| L1  | RX1NEG      |     |                                     |                                                                                                         |

| C1  | SGMIICLKP   | I   | LVDS                                | 125 MHz clock input to the SGMII PLL.                                                                   |

| D1  | SGMIICLKN   |     |                                     |                                                                                                         |

| E1  | SGMIICLK    | I   | TTL/CMOS                            | SGMII clock input. Maximum frequency 125 MHz + 100 ppm.                                                 |

| F8  | SGMIICLKSEL | I   | TTL <sup>U</sup> /CMOS <sup>U</sup> | SGMII clock select input.<br>Pull low for differential clock. Leave unconnected for single-ended clock. |

| R6  | MDC         | 0   | TTL                                 | MII clock.                                                                                              |

| V4  | MDIO        | I/0 | TTL                                 | MII data input/output.                                                                                  |

The pins of the SGMII interface are not 5 V tolerant.

NOTE: The SGMII data TX and RX differential pairs have 100  $\Omega$  resistors across them. External resistors are unnecessary.

#### Table 4 Time of day ports

| Pin | Symbol  | I/0 | Signal type | Description         |

|-----|---------|-----|-------------|---------------------|

| Т4  | UARTRX1 | I   | TTLD        | ToD1 receive data.  |

| R4  | UARTRXO | I   | TTLD        | ToDO receive data.  |

| R2  | UARTTX1 | 0   | TTL         | ToD1 transmit data. |

| V2  | UARTTXO | 0   | TTL         | ToDO transmit data. |

### Table 5Configuration pins

| Pin | Symbol   | I/0 | Signal type      | Description                             |

|-----|----------|-----|------------------|-----------------------------------------|

| G11 | SYSMODEO | Ι   | TTL <sub>D</sub> | Operating mode selection signal, bit 0. |

| G8  | SYSMODE1 | Ι   | TTL <sub>D</sub> | Operating mode selection signal, bit 1. |

#### Table 6 Input reference clocks (IPCLK0 to IPCLK17 are not 5 V tolerant and must be pulled low if not used)

| Pin | Symbol | I/0 | Signal type | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E11 | IPCLKO | I   | TTL         | Clock reference input 0, PTP or TDM module. Acceptable frequencies into the<br>PTP module from:<br>1 PPS/1 Hz to 161MHz (input reference for PTP Master).<br>Acceptable frequencies directly into the TDM module:<br>n × 8 kHz<br>1.544 MHz (SONET)/2.048 MHz (SDH)<br>6.48 MHz<br>19.44 MHz<br>25.92 MHz<br>38.88 MHz<br>51.84 MHz<br>77.76 MHz.<br>(Pull low if not used). |

| D11 | IPCLK1 | I   | TTL         | Clock reference input 1. PTP or TDM module.<br>Acceptable input frequencies as IPCLKO.<br>(Pull low if not used).                                                                                                                                                                                                                                                            |

| E10 | IPCLK2 | I   | TTL         | Clock reference input 2. PTP or TDM module.<br>Acceptable input frequencies as IPCLKO.<br>(Pull low if not used).                                                                                                                                                                                                                                                            |

| E9  | IPCLK3 | I   | TTL         | Clock reference input 3. PTP or TDM module.<br>Acceptable input frequencies as IPCLKO.<br>(Pull low if not used).                                                                                                                                                                                                                                                            |

| F10 | IPCLK4 | I   | TTL         | Clock reference input 4. PTP module only.<br>Acceptable input frequencies from 1 PPS/1 Hz to 161 MHz.<br>(Pull low if not used).                                                                                                                                                                                                                                             |

| D10 | IPCLK5 | I   | TTL         | Clock reference input 5. PTP module only.<br>Acceptable input frequencies from 1 PPS/1 Hz to 161 MHz.<br>(Pull low if not used).                                                                                                                                                                                                                                             |

**DAPU TELECOM**

Di

**FINAL**

| Table 6 Input ref | erence clocks (IPCLK0 | to IPCLK17 are not 5 | V tolerant and must be | pulled low if not used) |

|-------------------|-----------------------|----------------------|------------------------|-------------------------|

|-------------------|-----------------------|----------------------|------------------------|-------------------------|

| Pin | Symbol     | I/0 | Signal type      | Description                                                                                                                                                                                                                                                   |  |  |  |

|-----|------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| F11 | IPCLK6     | 1   | TTL              | Clock reference input 6. PTP module only.<br>Acceptable input frequencies from 1 PPS/1 Hz to 161 MHz.<br>(Pull low if not used).                                                                                                                              |  |  |  |

| D9  | IPCLK7     | I   | TTL              | Clock reference input 7. PTP module only.<br>Acceptable input frequencies from 1 PPS/1 Hz to 161 MHz.<br>(Pull low if not used).<br>Clock reference input 8. TDM module only.                                                                                 |  |  |  |

| K18 | IPCLK8NEG  | I   | LVPECL/<br>LVDS  | Clock reference input 8. TDM module only.<br>Differential input. Programmable input frequencies to a maximum of                                                                                                                                               |  |  |  |

| L18 | IPCLK8POS  |     | LVDS             | Differential input. Programmable input frequencies to a maximum of 155.52 MHz. Default 19.44 MHz. Default signal type LVDS.                                                                                                                                   |  |  |  |

| P17 | IPCLK9     | I   | AMI              | Clock reference input 9.<br>AMI, composite clock 64 kHz + 8 kHz (input reference for TDM Timing mode<br>only).<br>Default 64/8 kHz composite clock.                                                                                                           |  |  |  |

| N17 | IPCLK10    | I   | AMI              | Clock reference input 10.<br>AMI, composite clock 64 kHz + 8 kHz (input reference for TDM Timing mode<br>only).<br>Default 64/8 kHz composite clock.                                                                                                          |  |  |  |

| J18 | IPCLK11NEG | I   | LVPECL/          | Clock reference input 11. TDM module only.                                                                                                                                                                                                                    |  |  |  |

| H18 | IPCLK11POS |     | LVDS             | Differential input. Programmable input frequencies to a maximum of 155.52 MHz. Default 19.44 MHz. Default signal type LVPECL.                                                                                                                                 |  |  |  |

| J17 | IPCLK12    | 1   | ΠLD              | Clock reference input 12. TDM module only.<br>Acceptable frequencies directly into the TDM module:<br>n × 8 kHz<br>1.544 MHz (SONET)/2.048 MHz (SDH)<br>6.48 MHz<br>19.44 MHz<br>25.92 MHz<br>38.88 MHz<br>51.84 MHz<br>77.76 MHz.<br>(Pull low if not used). |  |  |  |

| H17 | IPCLK13    | I   | TTLD             | Clock reference input 13. TDM module only.<br>Acceptable input frequencies as IPCLK12.<br>(Pull low if not used).                                                                                                                                             |  |  |  |

| H16 | IPCLK14    | I   | ΠLD              | Clock reference input 14. TDM module only.<br>Acceptable input frequencies as IPCLK12.<br>(Pull low if not used).                                                                                                                                             |  |  |  |

| G16 | IPCLK15    | I   | TTL <sub>D</sub> | Clock reference input 15. TDM module only.<br>Acceptable input frequencies as IPCLK12.<br>(Pull low if not used).                                                                                                                                             |  |  |  |

| G17 | IPCLK16    | I   | TTL <sub>D</sub> | Clock reference input 16. TDM module only.<br>Acceptable input frequencies as IPCLK12.<br>(Pull low if not used).                                                                                                                                             |  |  |  |

| G18 | SYNC2K     | I   | TTLD             | Partner phase/frequency monitor.                                                                                                                                                                                                                              |  |  |  |

| J16 | IPCLK17    | I   | ΤΤL <sub>D</sub> | Clock reference input 17. TDM module only.<br>Acceptable input frequencies as IPCLK12.<br>(Pull low if not used).                                                                                                                                             |  |  |  |

### Table 7 Output reference clocks

| Pin | Symbol    | I/0 | Signal type     | Description                                                                                                                              |  |  |  |

|-----|-----------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R11 | OPCLKO    | 0   | TTL/CMOS        | For PTP mode operation, refer to Frequency and time generator.<br>For operation in TDM timing mode, refer to Table 43.                   |  |  |  |

| E7  | OPCLK1    | 0   | TTL/CMOS        | Clock reference output 1.<br>Same clock frequency configuration options as OPCLKO.                                                       |  |  |  |

| T11 | OPCLK2    | 0   | TTL/CMOS        | Clock reference output 2.<br>Same clock frequency configuration options as OPCLKO.                                                       |  |  |  |

| U11 | OPCLK3    | 0   | TTL/CMOS        | Clock reference output 3.<br>Same clock frequency configuration options as OPCLKO.                                                       |  |  |  |

| P18 | OPCLK4NEG | 0   | LVDS/           | Clock reference output 4.                                                                                                                |  |  |  |

| R18 | OPCLK4POS |     | LVPECL          | Default frequency 77.76 MHz.<br>Default signal type LVDS.                                                                                |  |  |  |

| N18 | OPCLK5NEG | 0   | LVDS/<br>LVPECL | Clock reference output 5.<br>Default frequency 155.52 MHz.<br>Default signal type LVPECL.                                                |  |  |  |

| M18 | OPCLK5POS |     | LVPECL          |                                                                                                                                          |  |  |  |

| U18 | OPCLK6NEG | 0   | AMI             | Clock reference output 6. TDM module only.                                                                                               |  |  |  |

| T18 | OPCLK6POS |     |                 | 64/8 kHz (composite clock, 64 kHz + 8 kHz).<br>Fixed frequency.                                                                          |  |  |  |

| H12 | OPCLK7    | 0   | TTL/CMOS        | Clock reference output 7. TDM module only.<br>Same clock frequency configuration options as OPCLKO.<br>For operation in TDM Timing mode. |  |  |  |

| P12 | OPCLK8    | 0   | TTL/CMOS        | Clock reference output 8. TDM module only.<br>Same clock frequency configuration options as OPCLK7.                                      |  |  |  |

| M17 | OPCLK9    | 0   | TTL/CMOS        | Clock reference output 9. TDM module only.<br>Same clock frequency configuration options as OPCLK7.                                      |  |  |  |

| L17 | OPCLK10   | 0   | TTL/CMOS        | Clock reference output 10. TDM module only.<br>Same clock frequency configuration options as OPCLK7.                                     |  |  |  |

#### Table 8 PPnS

| Pin | Symbol | I/0 | Signal type | Description                                                                                                                                                   |

|-----|--------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P11 | PPNSO  | 0   | TTL/CMOS    | Pulses per n second reference output. Default 1 pps.<br>Fully programmable high time: default 100 ms. <sup>1</sup><br>Rising edge specifies seconds rollover. |

| F7  | PPNS1  | 0   | TTL/CMOS    | Pulses per n second reference output. Default 1 pps.<br>Fully programmable high time: default 100 ms. <sup>1</sup><br>Rising edge specifies seconds rollover. |

1. May vary with software revision.

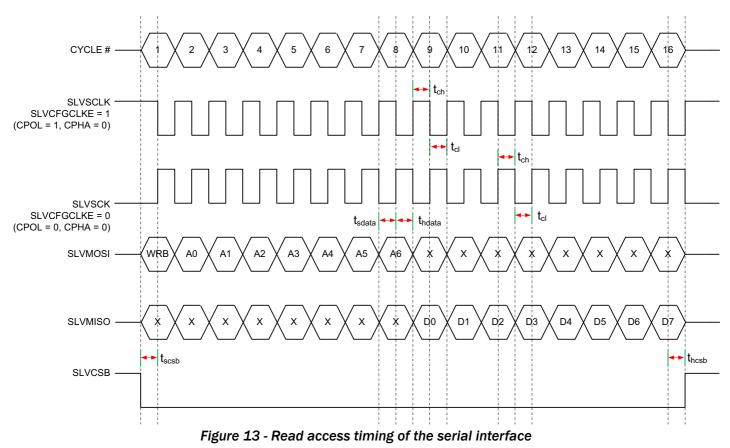

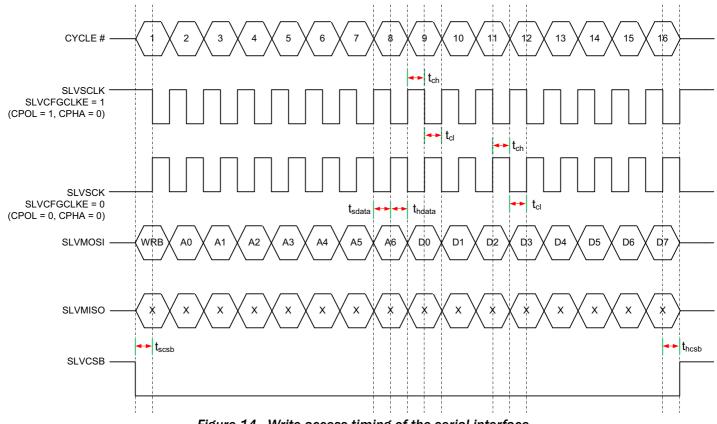

#### Table 9 Serial interfaces

| Pin | Symbol     | I/0 | Signal type        | Description                                                                                                                                                                                                                                                                                     |  |  |  |

|-----|------------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|     |            |     |                    | Slave SPI                                                                                                                                                                                                                                                                                       |  |  |  |

| K9  | SLVMISO    | 0   | TTL/CMOS           | Master in/slave out data output.                                                                                                                                                                                                                                                                |  |  |  |

| Т8  | SLVMOSI    | I   | TTL <sub>D</sub>   | Master out/slave in data input.                                                                                                                                                                                                                                                                 |  |  |  |

| М9  | SLVSCLK    | I   | TTL <sub>D</sub>   | Slave mode serial clock.                                                                                                                                                                                                                                                                        |  |  |  |

| 61  | SLVCSB     | I   | TTLU               | Chip select (slave):<br>0 = slave serial interface enabled.<br>1 = slave serial interface disabled.<br>Asserted by the microprocessor.                                                                                                                                                          |  |  |  |

| H8  | SLVINT     | 0   | TTL/CMOS           | Slave interrupt output:<br>0 = no interrupt.<br>1 = interrupt.                                                                                                                                                                                                                                  |  |  |  |

| M10 | SLVCFGCLKE | I   | ΠL <sub>D</sub>    | Clock control for slave serial interface:<br>0 = sampling of SLVMOSI occurs on the rising edge and clocking out of<br>SLVMISO occurs on the falling edge of SLVSCLK.<br>1 = sampling of SLVMOSI occurs on the falling edge and clocking out of<br>SLVMISO occurs on the rising edge of SLVSCLK. |  |  |  |

| L10 | SLVCFGSPI  | I   | TTLD               | For future use. Must be fitted with a 10 $k\Omega$ pull-down resistor.                                                                                                                                                                                                                          |  |  |  |

|     |            |     | 1                  | l <sup>2</sup> C                                                                                                                                                                                                                                                                                |  |  |  |

| К12 | SCL        | 0   | CMOS open<br>drain | I2C SCL for the interface to ACS1790.                                                                                                                                                                                                                                                           |  |  |  |

| K8  | SDA        | I/0 | CMOS open<br>drain | I2C SDA for the interface to ACS1790.                                                                                                                                                                                                                                                           |  |  |  |

#### Table 10 System clocks

| Pin | Symbol                                                                                                                 | I/0 | Signal type | Description |  |

|-----|------------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|--|

|     | Local oscillator                                                                                                       |     |             |             |  |

| C10 | C10 REFCLK I TTL Input for local oscillator in normal operating mode.<br>Expected input frequency set by OSC_SEL[1:0]. |     |             |             |  |

If REFCLK is not supplied by a good quality oscillator, the ACS9522 may still appear to work but performance may be seriously compromised.

DPSync ACS9522

FINAL

## Table 11 Power supply pins

| Pin | Symbol        | Description                     | Pin | Symbol | Description      |

|-----|---------------|---------------------------------|-----|--------|------------------|

| L2  | VDDASGMIIRXO  | 1.2 V SGMII RX analogue supply. | C2  | VDDIO  | 3.3 V I/O supply |

| P2  | VDDASGMIITXO  | 1.2 V SGMII TX analogue supply. | C12 |        |                  |

| M2  | VDDHASGMIIRXO | 3.3 V SGMII RX analogue supply. | D2  |        |                  |

| N2  | VDDHASGMIITXO | 3.3 V SGMII TX analogue supply. | D12 |        |                  |

| МЗ  | VDDSGMIIO     | 1.2 V SGMII digital supply.     | D18 |        |                  |

| K2  | VDDASGMIIRX1  | 1.2 V SGMII RX analogue supply. | E12 |        |                  |

| G2  | VDDASGMIITX1  | 1.2 V SGMII TX analogue supply. | E18 |        |                  |

| J2  | VDDHASGMIIRX1 | 3.3 V SGMII RX analogue supply. | F5  |        |                  |

| H2  | VDDHASGMIITX1 | 3.3 V SGMII TX analogue supply. | F6  |        |                  |

| K3  | VDDSGMII1     | 1.2 V SGMII digital supply.     | F12 |        |                  |

| J4  | VDDCORE       | 1.2 V digital supply.           | F18 |        |                  |

| J5  |               |                                 | G4  |        |                  |

| J6  |               |                                 | G5  |        |                  |

| J8  |               |                                 | G6  |        |                  |

| L9  |               |                                 | G12 |        |                  |

| P5  |               |                                 | G14 |        |                  |

| P7  |               |                                 | G15 |        |                  |

| R5  |               |                                 | H5  |        |                  |

| R7  |               |                                 | H6  |        |                  |

| T1  | VDDCMUD       | 1.2 V digital supply for CMU    | H11 |        |                  |

| T2  |               |                                 | J14 |        |                  |

| U1  | VDDCMU        | 3.3 V analogue supply for CMU   | K5  |        |                  |

| U2  |               |                                 | K6  |        |                  |

| U14 | ESVA1         | 3.3 V analogue PLL supply       | K7  |        |                  |

| V17 | ESVA2         |                                 | K10 |        |                  |

| P13 | ESVA3         |                                 | K11 |        |                  |

| B2  | VDDIO         | 3.3 V I/O supply                | N10 |        |                  |

| B12 |               |                                 | P4  |        |                  |

| B13 |               |                                 | P6  |        |                  |

| B14 |               |                                 | P8  |        |                  |

| B15 |               |                                 | P10 |        |                  |

| B16 |               |                                 | R3  |        |                  |

| B17 |               |                                 | U4  |        |                  |

### Table 11 Power supply pins

| Pin | Symbol   | Description           |

|-----|----------|-----------------------|

| V11 | VDDIO    | 3.3 V I/O supply      |

| K14 | VDD_SETS | 3.3 V supply for SETS |

| K15 |          |                       |

| K16 |          |                       |

| K17 |          |                       |

| L12 |          |                       |

| Pin | Symbol   | Description           |

|-----|----------|-----------------------|

| M16 | VDD_SETS | 3.3 V supply for SETS |

| N16 |          |                       |

| P16 |          |                       |

| R16 |          |                       |

| U13 |          |                       |

ACS9522

FINAL

### Table 12 Ground pins

| Pin | Symbol | Description          | Pin | Symbol | Description |

|-----|--------|----------------------|-----|--------|-------------|

| P3  | GNDCMU | Digital PLL ground.  | E5  | VSS    |             |

| R13 | ESGNDA | Analogue PLL ground. | E6  |        |             |

| V13 |        |                      | E13 |        |             |

| U17 |        |                      | E14 |        |             |

| A1  | VSS    |                      | E15 |        |             |

| A2  |        |                      | E16 |        |             |

| A3  |        |                      | E17 |        |             |

| A18 |        |                      | F1  |        |             |

| B1  |        |                      | F13 |        |             |

| В3  |        |                      | F14 |        |             |

| B4  |        |                      | F15 |        |             |

| B5  |        |                      | F16 |        |             |

| B6  |        |                      | F17 |        |             |

| B18 |        |                      | G1  |        |             |

| C3  |        |                      | J10 |        |             |

| C4  |        |                      | J11 |        |             |

| C5  |        |                      | L4  |        |             |

| C6  |        |                      | L5  |        |             |

| C13 |        |                      | L6  |        |             |

| C14 |        |                      | L7  |        |             |

| C15 |        |                      | L8  |        |             |

| C16 |        |                      | L11 |        |             |

| C17 |        |                      | L13 |        |             |

| C18 |        |                      | L14 |        |             |

| D3  |        |                      | L15 |        |             |

| D4  |        |                      | L16 |        |             |

| D5  |        |                      | M4  |        |             |

| D6  |        |                      | M5  |        |             |

| D13 |        |                      | M6  |        |             |

| D14 |        |                      | M7  |        |             |

| D15 |        |                      | M8  |        |             |

| D16 |        |                      | M11 |        |             |

| D17 |        |                      | M13 |        |             |

| E4  |        |                      | M14 |        |             |

### Table 12 Ground pins

| Pin | Symbol | Description | Pin | Symbol    | Description |

|-----|--------|-------------|-----|-----------|-------------|

| M15 | VSS    |             | R14 | VSS       |             |

| N4  |        |             | R15 |           |             |

| N5  |        |             | T13 |           |             |

| N6  |        |             | T14 |           |             |

| N7  |        |             | T15 |           |             |

| N8  |        |             | T16 |           |             |

| N9  |        |             | V1  |           |             |

| N13 |        |             | V18 |           |             |

| N14 |        |             | L3  | VSSSGMIIO |             |

| N15 |        |             | N3  |           |             |

| P14 |        |             | J3  | VSSSGMII1 |             |

| P15 |        |             | K4  |           |             |

## Table 13 Internally connected pins

| Pin             | Symbol | Description     | Pin             | Symbol | Description     |

|-----------------|--------|-----------------|-----------------|--------|-----------------|

| A4              | IC 01  | Leave to float. | R8 <sup>1</sup> | IC 27  | Leave to float. |

| A5              | IC 02  |                 | R9              | IC 28  |                 |

| A13             | IC 03  |                 | R12             | IC 29  |                 |

| A17             | IC 04  |                 | R17             | IC 30  |                 |

| C11             | IC 05  |                 | T3 1            | IC 31  |                 |

| D8              | IC 06  |                 | T5 <sup>1</sup> | IC 32  |                 |

| E2              | IC 07  |                 | T6 <sup>1</sup> | IC 33  |                 |

| E3              | IC 08  |                 | T7 <sup>1</sup> | IC 34  |                 |

| E8              | IC 09  |                 | Т9              | IC 35  |                 |

| F2              | IC 10  |                 | T12             | IC 36  |                 |

| F4              | IC 11  |                 | T17             | IC 37  |                 |

| G3              | IC 12  |                 | U3 1            | IC 38  |                 |

| G9              | IC 13  |                 | U5 1            | IC 39  |                 |

| G10             | IC 14  |                 | U61             | IC 40  |                 |

| G13             | IC 15  |                 | U7 1            | IC 41  |                 |

| НЗ              | IC 16  |                 | U8 1            | IC 42  |                 |

| H4              | IC 17  |                 | U10             | IC 43  |                 |

| H13             | IC 18  |                 | U15             | IC 44  |                 |

| H14             | IC 19  |                 | V3 1            | IC 45  |                 |

| H15             | IC 20  |                 | V5              | IC 46  |                 |

| J13             | IC 21  |                 | V6 <sup>1</sup> | IC 47  |                 |

| J15             | IC 22  |                 | V7 1            | IC 48  |                 |

| К13             | IC 23  |                 | V8 1            | IC 49  |                 |

| N11             | IC 24  |                 | V9              | IC 50  |                 |

| N12             | IC 25  |                 | V12             | IC 51  |                 |

| P9 <sup>1</sup> | IC 26  |                 |                 |        |                 |

1.

### Table 14 Not connected pins

| Pin | Symbol | Description    | Pin | Symbol | Description    |

|-----|--------|----------------|-----|--------|----------------|

| A6  | NC     | Leave to float | B7  | NC     | Leave to float |

| A7  |        |                | B8  |        |                |

| A8  |        |                | B9  |        |                |

| A9  |        |                | B10 |        |                |

| A10 |        |                | B11 |        |                |

| A11 |        |                | C7  |        |                |

| A12 |        |                | C8  |        |                |

| A14 |        |                | C9  |        |                |

| A15 |        |                | D7  |        |                |

| A16 |        |                | F3  |        |                |

# Interfaces

This section describes the various interfaces provided on the ACS9522.

## Input reference clocks

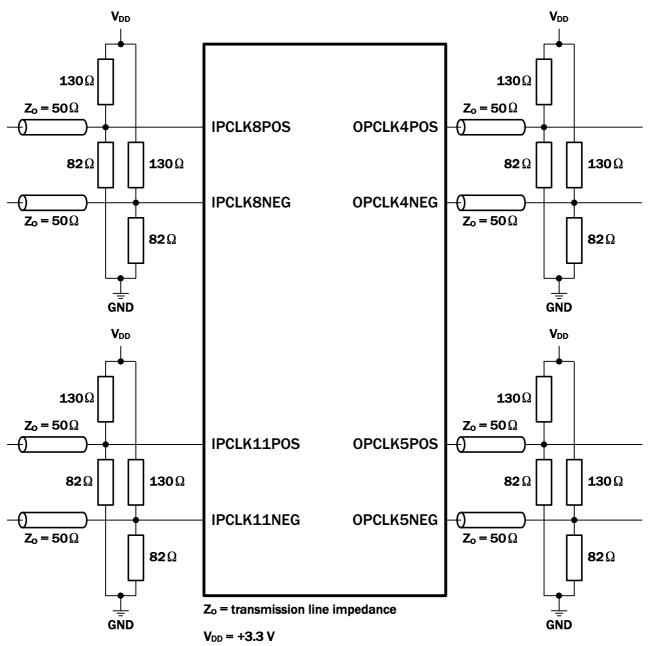

There are 18 clock reference inputs denoted IPCLK[17:0], using these variety of I/O technologies:

- AMI (for Alternate Mark Inversion signals)

- LVPECL/LVDS

- LVTTL

## AMI input and output ports

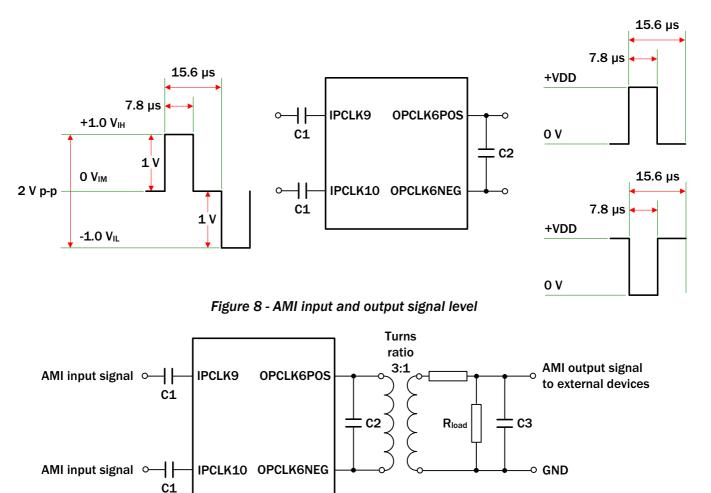

Input clocks IPCLK9 and IPCLK10 are for AMI composite 64 kHz/8 kHz clocks. The composite clock timing signals convey the 64 kHz bit-timing information using AMI coding with a 50% to 70% duty ratio and the 8 kHz octet phase information by introducing violations in the code rule. The structure of the signals and the voltage levels are shown in Figure 8 and Figure 9.

The AMI signal is DC balanced, and consists of positive and negative pulses with a peak-to-peak voltage of 2.0 ±0.2 V.

The electrical specifications are obtained from the digital 64 kbit/s centralized clock interface.

The 400 Hz component is not supported.

The electrical characteristics of the 64 kbit/s interface are as follows:

- Nominal bit rate: 64 kbit/s. The tolerance is determined by the network clock stability.

- There should be a symmetrical pair carrying the composite timing signal (64 kHz and 8 kHz). The use of transformers is recommended.

- For the over-voltage protection requirement, refer to ITU Recommendation K.41<sup>21</sup>.

#### Table 15 DC characteristics of the AMI input and output ports

Across all operating conditions, unless otherwise stated.

| Parameter                                          | Symbol               | Minimum                | Typical | Maximum               | Units |

|----------------------------------------------------|----------------------|------------------------|---------|-----------------------|-------|

| Input pulse width.                                 | t <sub>PW</sub>      | 1.56                   | 7.8     | 14.04                 | μs    |

| Input pulse rise/fall time.                        | t <sub>R/F</sub>     | -                      | -       | 5                     | μs    |

| AMI input voltage high.                            | V <sub>IH AMI</sub>  | 2.5                    | -       | V <sub>DD</sub> + 0.3 | V     |

| AMI input voltage middle.                          | V <sub>VIM AMI</sub> | 1.5                    | 1.65    | 1.8                   | V     |

| AMI input voltage low.                             | V <sub>VIL AMI</sub> | 0                      | -       | 1.4                   | V     |

| AMI output current drive.                          | I <sub>AMIOUT</sub>  | -                      | -       | 20                    | mA    |

| AMI output high voltage.<br>Output current = 20mA. | V <sub>OH AMI</sub>  | V <sub>DD</sub> - 0.16 | -       | -                     | V     |

| AMI output low voltage.<br>Output current = 20mA.  | V <sub>OL AMI</sub>  | -                      | -       | 0.16                  | V     |

| Output pulse width                                 | tPW_out              | -                      | 7.8     | -                     | μs    |

| Nominal test load impedance.                       | R <sub>TEST</sub>    | -                      | 110     | -                     | Ω     |

| "Mark" amplitude after transformer.                | V <sub>MARK</sub>    | 0.9                    | 1.0     | 1.1                   | V     |

| "Space" amplitude after transformer.               | V <sub>SPACE</sub>   | - 0.1                  | 0       | 0.1                   | V     |

# DPSync ACS9522

FINAL

#### Signal structure of 64 kHz/8 kHz central clock interface after suitable transformer

Figure 9 - Recommended line termination for the AMI input and output ports