# DAP8201M(I) —A Fast Ethernet PHY Series

### **Overview**

This device directly connects to the MAC layer through MII or RMII and supports MII/RMII to Copper.

The DAP8201M(I) is designed for easy implementation of 10/100Mbps Ethernet LANs. The MDI ports interfaces directly to CAT5 twisted pair media cable through the external transformer.

The DAP8201M(I) supports single 3.3V power supply.

Designed for low power, Wake-on-LAN can be used to lower system power consumption. The DAP8201M(I) is suitable for a wide range of applications.

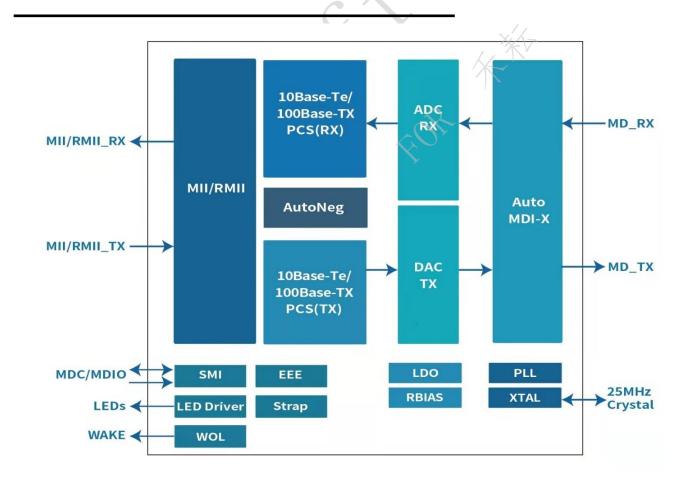

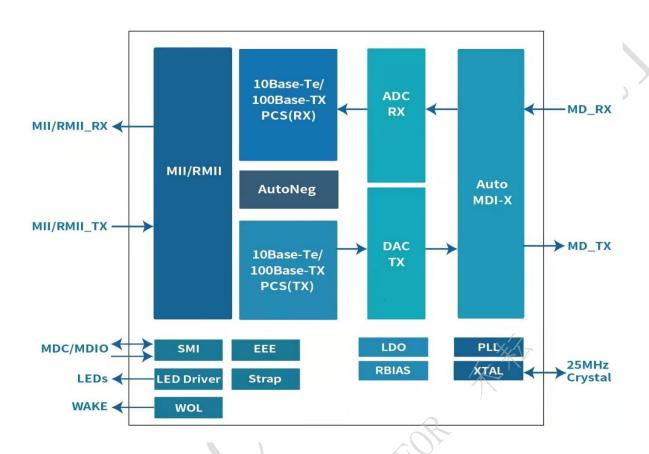

### **Block Diagram**

1

DAPU

## **Key Features**

- MII and RMII MAC Interface Options

- MII to Copper, RMII to Copper

- 100Base-TX/10Base-Te IEEE 802.3 Compliant

- IEEE 802.3az-2010 (EEE) Compliant

- WoL (Wake-on-LAN)

- Power Down Mode

- Auto-negotiation

- Auto-MDI-X

- Automatic Polarity Correction

- Supports Base Line Wander Correction

- Supports Interrupt Function

- 2 LEDs for Network Status

- Supports 25MHz External Crystal or 25M OSC Clock Input

- Output 50MHz Clock For MAC

- Integrate Linear Regulator 1.2V

- MAC I/O Voltage :3.3V

- 3.3V Single Power Supply

- Operation Temperature Range:

$$0^{\circ}C \sim +70^{\circ}C$$

$$-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$$

• Package: QFN 32-pin 5mm x 5mm

| Part Number | MII to | RMII   | WoL | 100Base-TX | 10Base-Te | EEE | Integrated | Temp.         | Package |

|-------------|--------|--------|-----|------------|-----------|-----|------------|---------------|---------|

|             | Copper | to     |     |            |           |     | LDO        | 1,            |         |

|             |        | Copper |     |            |           |     |            | XXX           |         |

| DAP8201M    | •      | •      | •   | •          | •         | •   | • //       | 0°C ~ +70°C   | QFN32   |

| DAP8201MI   |        | •      | •   | •          | •         | •   | •          | -40°C ~ +85°C | QFN32   |

●: Support

# **Applications**

- Enterprise & SOHO

- LED Display

- Industrial Embedded Computing

- Wired and Wireless Communications Infrastructure

- Consumer Electronics

# **Revision History**

| Revision | Change Contents                                                                                                                                        | Prepared by | Revised Date |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|

| 1.0      | First Issued                                                                                                                                           |             | 2022.03.05   |

| 1.1      | Correct some inexact description: delete the internal power-on-reset; correct the absolute power supply voltage; correct pin name: $V_{DD\_1V}$ ; etc. |             | 2022.04.16   |

| 1.2      | Add DAP8201MI Correct description: LED1, Link 100Mbps On; LED_ACT_LEVEL_TH default value is 0xC PKG_IPG_LENGTH default value is 0xC;                   |             | 2022.05.31   |

|          | Table 15: bit 15 reset's description;                                                                                                                  |             |              |

|          |                                                                                                                                                        | **\_        |              |

|          |                                                                                                                                                        | *           |              |

|          | Ž <sub>O</sub> ,                                                                                                                                       |             |              |

|          |                                                                                                                                                        |             |              |

|          |                                                                                                                                                        |             |              |

# Index

| 0 | VER  | VIEW.    |                               |          | 1    |

|---|------|----------|-------------------------------|----------|------|

| В | LOC  | K DIA    | GRAM                          |          | 1    |

| K | EY F | EATUI    | RES                           |          | 2    |

| R | EVIS | SION H   | ISTORY                        |          | 3    |

| I | NDEX | ζ        |                               |          | 4    |

| 1 |      | PIN DEF  | INITION                       | 7        | 8    |

| 2 |      |          |                               | X        | 11   |

| _ | 2.1  |          |                               |          |      |

|   |      |          |                               |          |      |

|   | 2.2  |          |                               |          |      |

|   | 2.3  |          |                               |          |      |

|   | 2.4  | DC C     | HARACTERISTICS                |          | . 13 |

|   | 2.5  | TIMIN    | IG CHARACTERISTICS            |          | 13   |

|   | 2    | .5.1     |                               | , X      |      |

|   | 2    | .5.2     | MII Interface Timing          |          | . 14 |

|   | 2    | .5.3     |                               |          |      |

|   | 2.6  | Refer    | RENCE CLOCK REQUIREMENTS      | <u>R</u> | . 17 |

| 3 | I    | DETAIL I | DESCRIPTION                   |          | . 18 |

|   | 3.1  | Bloci    | K DIAGRAM                     |          | 18   |

|   | 3.2  |          |                               |          |      |

|   |      | .2.1     |                               |          |      |

|   |      | .2.2     |                               |          |      |

|   |      |          |                               |          |      |

|   |      | .2.3     | Auto-MDIX                     |          | . 20 |

|   | 3    | .2.4     | Automatic Polarity Correction |          | . 20 |

|   | 3    | .2.5     | IEEE 802.3az-2010 EEE         |          | . 20 |

|   | 3    | .2.6     | UTP Ethernet                  |          | . 20 |

|   | 3    | .2.7     | MII Interface                 |          | . 20 |

|   | 3.2.8     | RMII Interface                                                             | 2          |

|---|-----------|----------------------------------------------------------------------------|------------|

|   | 3.2.9     | Reverse MII Interface                                                      | 22         |

|   | 3.2.10    | Loopback Mode                                                              | 22         |

|   | 3.2.11    | Hardware Bootstrap Configuration                                           | <b>2</b> 3 |

|   | 3.2.12    | Reset                                                                      | 23         |

|   | 3.2.13    | Power Supply                                                               | 23         |

| 4 | REGIST    | ERS                                                                        | 25         |

|   | 4.1 REGIS | STER MAPPING                                                               | 25         |

|   | 4.2 REGIS | STER ACCESS TYPES                                                          | 25         |

|   | 4.3 BASIO | C REGISTER                                                                 | 25         |

|   | 4.3.1     | BMCR(Basic Mode Control Register,Address: Register 0x0)                    | 26         |

|   | 4.3.2     | BMSR (Basic Mode Status Register,Address: Register 0x1 )                   | 27         |

|   | 4.3.3     | PHYID1 (PHY Identifier Register #1, Address: Register 0x2)                 | 28         |

|   | 4.3.4     | PHYID2 (PHY Identifier Register #2 , Address: Register 0x3 )               | 28         |

|   | 4.3.5     | ANAR (Auto-Negotiation Advertising , Address: Register 0x4 )               | 28         |

|   | 4.3.6     | ANLPA (Auto-Negotiation Link Partner Ability, Address: Register 0x5)       | 29         |

|   | 4.3.7     | ANE (Auto-Negotiation Expansion Register Address: Register 0x6)            | 30         |

|   | 4.3.8     | ANNPT (Auto-Negotiation Next Page Transmit Register Address: Register 7)   | 30         |

|   | 4.3.9     | ANNPR (Auto-Negotiation Next Page Received Register Address: Register 0x8) | 3          |

|   | 4.3.10    | MSSR (Master-Slave Status Register Address: Register 0xA)                  | 31         |

|   | 4.3.11    | MMD_AC (MMD Access Control; Address: Register 0xD)                         | 32         |

|   | 4.3.12    | MMD_AADA (MMD Access Address Data, Address: Register 0xE)                  | 32         |

|   | 4.3.13    | PHYCR (PHY Control Register, Address: Register 0x10)                       | 32         |

|   | 4.3.14    | PHYSR (PHY Status Register, Address: Register 0x11)                        | <b>3</b> 3 |

|   | 4.3.15    | INTCR (Interrupt Control Register, Address: Register 0x12)                 | 34         |

|   | 4.3.16    | INTSR (Interrupt Status Register, Address: Register 0x13)                  | 35         |

|   | 4.3.17    | SPCR (Speed Configuration Register, Address: Register 0x14)                | 35         |

|   | 4.3.18    | RECR (Receiver Error Counter Register, Address: Register 0x15)             | 36         |

|   |           |                                                                            |            |

|    | 4.3.19  | EXT_ADD (Extended Register Address Register, Address: Register 0x1E)       | 36 |

|----|---------|----------------------------------------------------------------------------|----|

|    | 4.3.20  | EXT_DATA (Extended Register Data Register, Register 0x1F)                  | 36 |

| 1. | 4 Ехтег | NDED REGISTER                                                              | 36 |

|    | 4.4.1   | EXT_10M_PWRCON (10Mbps Power Control Register, Address: Register 0x200A)   | 36 |

|    | 4.4.2   | EXT_COMBO_CON (COMBO Control Register, Address: Register 0x4000)           | 36 |

|    | 4.4.3   | EXT_PIN_CON (PAD Control Register, Address: Register 0x4001)               | 37 |

|    | 4.4.4   | EXT_COMBO2_CON (COMBO2 Control Register, Address: Register 0x4003)         | 37 |

|    | 4.4.5   | WoL_MAC_ADDH(WoL MAC Highest Address Register, Address: Register 0x4004)   | 38 |

|    | 4.4.6   | WoL_MAC_ADDM(WoL MAC Middle Address Register, Address: Register 0x4005)    | 38 |

|    | 4.4.7   | WoL_MAC_ADDL(WoL MAC Lowest Address Register, Address: Register 0x4006)    | 38 |

|    | 4.4.8   | PKG_ST_CON (Package Generation Selftest Control, Address: Register 0x40A0) | 38 |

|    | 4.4.9   | PKG_LEN(Package Generation Length, Address: Register 0x40A1)               | 39 |

|    | 4.4.10  | PKG_BS(Package Generation Burst Size, Address: Register 0x40A2)            | 39 |

|    | 4.4.11  | PKG_RV_H(Package Receiver Valid High, Address: Register 0x40A3)            | 39 |

|    | 4.4.12  | PKG_RV_L(Package Receiver Valid Low, Address: Register 0x40A4)             | 40 |

|    | 4.4.13  | PKG_RX_OSH(Package Receiver OS High, Address: Register 0x40A5)             | 40 |

|    | 4.4.14  | PKG_RX_OSL(Package Receiver OS Low, Address: Register 0x40A6)              | 40 |

|    | 4.4.15  | PKG_RX_USH(Package Receiver US High, Address: Register 0x40A7)             | 40 |

|    | 4.4.16  | PKG_RX_USL(Package Receiver US Low, Address: Register 0x40A8)              | 40 |

|    | 4.4.17  | PKG_RX_ERR(Package Receiver Error, Address: Register 0x40A9)               | 40 |

|    | 4.4.18  | PKG_RX_OS_ERR(Package Receiver OS Error, Address: Register 0x40AA)         | 41 |

|    | 4.4.19  | PKG_RX_FRM (Package Receiver Fragment, Address: Register 0x40AB)           | 41 |

|    | 4.4.20  | PKG_RX_NOSFD(Package Receiver NOSFD, Address: Register 0x40AC)             | 41 |

|    | 4.4.21  | PKG_TV_H(Package Transmit Valid High, Address: Register 0x40AD)            | 41 |

|    | 4.4.22  | PKG_TV_L(Package Transmit Valid Low, Address: Register 0x40AE)             | 41 |

|    | 4.4.23  | PKG_TX_OSH(Package Transmit OS High, Address: Register 0x40AF)             | 41 |

|    | 4.4.24  | PKG_TX_OSL(Package Transmit OS Low, Address: Register 0x40B0)              | 42 |

|    | 4.4.25  | PKG_TX_USH(Package Transmit US High, Address: Register 0x40B1)             | 42 |

|    |         |                                                                            |    |

| 6 | DIMEN  | ISIONS                                                             | 48 |

|---|--------|--------------------------------------------------------------------|----|

| 5 | ENVIRO | ONMENT                                                             | 47 |

|   | 4.4.38 | LED1_CON (LED1 Control Register, Address: Register 0x40C3)         | 46 |

|   | 4.4.37 | LED_BLCON (LED Blink Control Register, Address: Register 0x40C2)   | 45 |

|   | 4.4.36 | LED_COMCON (LED Common Control Register, Address: Register 0x40C1) | 44 |

|   | 4.4.35 | LEDO_CON (LEDO Control Register, Address: Register 0x40C0)         | 44 |

|   | 4.4.34 | PKG_CON5 (Package Generation Configure5, Address: Register 0x40BA) | 43 |

|   | 4.4.33 | PKG_CON4 (Package Generation Configure4, Address: Register 0x40B9) | 43 |

|   | 4.4.32 | PKG_CON3 (Package Generation Configure3, Address: Register 0x40B8) | 43 |

|   | 4.4.31 | PKG_CON2 (Package Generation Configure2, Address: Register 0x40B7) | 43 |

|   | 4.4.30 | PKG_TX_NOSFD (Package Transmit NOSFD, Address: Register 0x40B6)    | 43 |

|   | 4.4.29 | PKG_TX_FRM (Package Transmit Fragment, Address: Register 0x40B5)   | 42 |

|   | 4.4.28 | PKG_TX_OS_ERR(Package Transmit OS Error, Address: Register 0x40B4) | 42 |

|   | 4.4.27 | PKG_TX_ERR(Package Transmit Error, Address: Register 0x40B3)       | 42 |

|   | 4.4.26 | PKG_TX_USL(Package Transmit US Low, Address: Register 0x40B2)      | 42 |

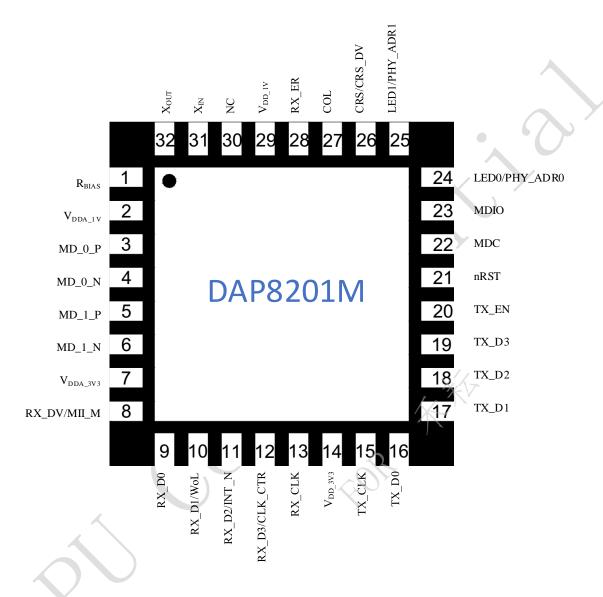

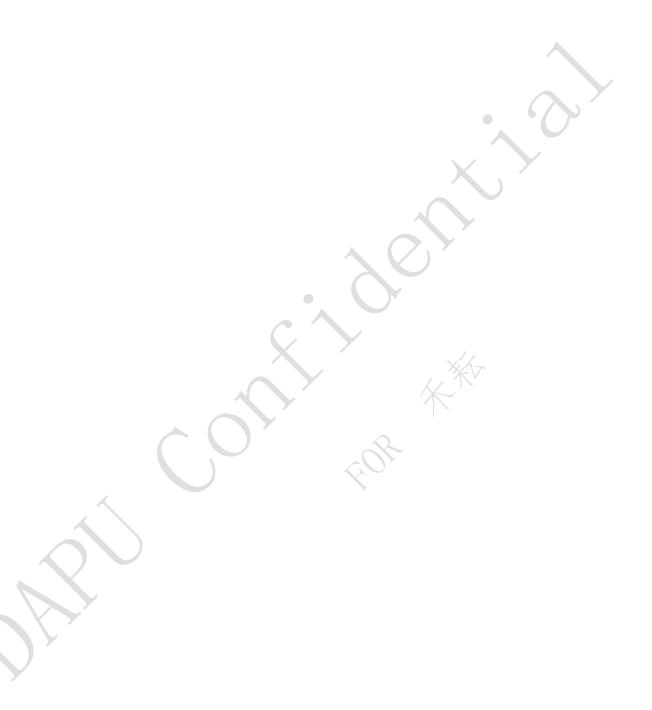

### 1 Pin Definition

Figure 1 Package 32-Pin (Top View)

Table 1. Pin Definition

| Pin<br>Number | Pin Name         | I/O   | Description                                                                                      |  |  |  |  |

|---------------|------------------|-------|--------------------------------------------------------------------------------------------------|--|--|--|--|

|               | POWER AND GROUND |       |                                                                                                  |  |  |  |  |

| 2             | $V_{DDA\_1V}$    | PWR/O | Power Output. Be sure to connect a 0.1µF and a 1.0uF ceramic capacitors for decoupling purposes. |  |  |  |  |

| 7             | $V_{DDA\_3V3}$   | PWR   | 3.3V Analog Supply Input. A 1µF and 0.1µF capacitor are required to GND.                         |  |  |  |  |

| 14            | $V_{DD\_3V3}$    | PWR   | 3.3V Digital Supply Input. Digital I/O power input for MII/RMII I/O, MDC/MDIO                    |  |  |  |  |

| 29 | $V_{\mathrm{DD\_1V}}$ | PWR/O   | Power Output. Be sure to connect a 0.1µF and a 1.0uF ceramic capacitors for decoupling purposes.                                                                                                                                                                                                                   |

|----|-----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33 | EPAD                  | GND     | Ground                                                                                                                                                                                                                                                                                                             |

| 33 | Elitib                |         | FERENCE CLOCK                                                                                                                                                                                                                                                                                                      |

| 31 | X <sub>IN</sub>       | I       | Crystal/Oscillator Input: 25MHz oscillator or 25MHz crystal input                                                                                                                                                                                                                                                  |

| 32 | X <sub>OUT</sub>      | 0       | Crystal Output: 25MHz crystal. Must be left floating if use oscillator.                                                                                                                                                                                                                                            |

|    |                       | MEDIA D | EPENDENT INTERFACE                                                                                                                                                                                                                                                                                                 |

| 3  | MD_0_P                | I/O     | Differential Transmit/Receive. These differential IOs are automatically configured to either 10Base-Te or 100Base-TX signaling.                                                                                                                                                                                    |

| 4  | MD_0_N                | I/O     | Auto-MDIX mode: it can be used as the Receive Input pair. There are $50\Omega$ internal terminations on each pin, and due to this device incorporates voltage driven DAC, it does not require a center-tap power supply.                                                                                           |

| 5  | MD_1_P                | I/O     | Differential Transmit/Receive. These differential IOs are automatically configured to either 10Base-Te or 100Base-TX signaling.                                                                                                                                                                                    |

| 6  | MD_1_N                | I/O     | Auto-MDIX mode: it can be used as the Receive Input pair. There are $50\Omega$ internal terminations on each pin, and due to this device incorporates voltage driven DAC, it does not require a center-tap power supply.                                                                                           |

|    | I .                   | MANA    | GEMENT INTERFACE                                                                                                                                                                                                                                                                                                   |

| 21 | nRST                  | I/HZ    | Reset: The active low RESET initializes or reinitializes the PHY, then all internal registers reinitialize to the default state.  Note: The reset signal must be held low at least 10ms.                                                                                                                           |

| 22 | MDC                   | I/PU    | Management Data Clock                                                                                                                                                                                                                                                                                              |

| 23 | MDIO                  | I/O/PU  | Input/Output of Management Data.                                                                                                                                                                                                                                                                                   |

|    | ,                     | M       | II/RMII Interface                                                                                                                                                                                                                                                                                                  |

| 15 | TX_CLK                | I/O/PD  | MII Mode: MII transmit clock, MII transmit clock provides a 25MHz reference clock for 100Mbps and a 2.5MHz reference clock for 10Mbps.  RMII Mode: RMII Reference Clock, 50MHz input or output for both transmit and receive.  The default direction is reference clock output mode if RX_D3/CLK_CTR pin floating. |

| 20 | TX_EN                 | I/PD    | Transmit enable: TX_EN is presented on the rising edge of the TX_CLK.  MII Mode: TX_EN indicates the presence of valid data inputs on TX_D[3:0]  RMII Mode: TX_EN indicates the presence of valid data inputs on TX_D[1:0]  TX_EN is an active high signal.                                                        |

| 16 | TX_D0                 | I/PD    |                                                                                                                                                                                                                                                                                                                    |

| 17 | TX_D1                 | I/PD    | Transmit Data. The MAC will source TXD [0:3] synchronous with TXC when TX_EN is asserted.                                                                                                                                                                                                                          |

| 18 | TX_D2                 | I/PD    |                                                                                                                                                                                                                                                                                                                    |

| 19 | TX_D3                 | I/PD    |                                                                                                                                                                                                                                                                                                                    |

| 13 |                  |         |                                                                                                                                                                                                                                                                                                                                                                                           |                                          |                                                                                                                      |  |  |  |

|----|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| 8  | RX_DV/MII_M      | O/LI/PD | speed, which is derived from the received data stream.  Receive data valid: This pin indicates valid data is present on the RX_D[3:0] for MII mode.  Hardware Bootstrap for Media Mode Select with Pin13,  0: MII 1: RMII  Pin8   Pin12   Media Mode  0   0   MII  0   1   Reverse MII  1   0   RMII2(TX_CLK outputs 50MHz Reference clock by default)  1   1   RMII1(TX_CLK inputs 50MHz |                                          |                                                                                                                      |  |  |  |

| 28 | RX_ER            | O/PD    | Reference clock  Receive error: This pin indicates that an error symbol has been detected within a received packet in both MII and RMII mode. In MII mode, RX_ER is asserted high synchronously to the rising edge of RX_CLK.                                                                                                                                                             |                                          |                                                                                                                      |  |  |  |

| 9  | RX_D0            | O/PD    | presented o                                                                                                                                                                                                                                                                                                                                                                               | n these pins                             | s received on the cable are decoded and s synchronous to the rising edge of DV is asserted, they contain valid data. |  |  |  |

| 10 | RX_D1/WoL        | O/LI/PD | Receive data: Symbols received on the cable are decoded and presented on these pins synchronous to the rising edge of RX_CLK. When RX_DV is asserted, they contain valid data. Hardware Bootstrap:  0: Pin24 works as LED0  1: Pin24 works as WoL, must be pulled up.                                                                                                                     |                                          |                                                                                                                      |  |  |  |

| 11 | RX_D2/nINT       | O/OD/PD | Receive data: Symbols received on the cable are decoded and presented on these pins synchronous to the rising edge of RX_CLK. When RX_DV is asserted, they contain valid data. MII Mode: A RX_D[3:0] is received RMII Mode:RX_D2 is used for interrupt pin.                                                                                                                               |                                          |                                                                                                                      |  |  |  |

| 12 | RX_D3/TX_CLK_CTR | O/LI/PD | Receive data: Symbols received on the cable are decoded and presented on these pins synchronous to the rising edge of RX_CLK. When RX_DV is asserted, they contain valid data. Hardware Bootstrap(RMII TX Clock control):  0: RMII TX_CLK output, 1: RMII TX_CLK input                                                                                                                    |                                          |                                                                                                                      |  |  |  |

| 26 | CRS/CRS_DV       | O/PD    | MII Mode:<br>medium is                                                                                                                                                                                                                                                                                                                                                                    | Carrier Ser<br>non-idle.<br>e: This sign | al combines the RMII Carrier Sense and                                                                               |  |  |  |

| 27 | COL              | O/PD    | Collision detect: In MII mode: For Full-Duplex mode, this pin is always low. In Half Duplex mode, this pin is asserted high only when both transmit and receive media are non-idle.                                                                                                                                                                                                       |                                          |                                                                                                                      |  |  |  |

|    | LED              |         |                                                                                                                                                                                                                                                                                                                                                                                           |                                          |                                                                                                                      |  |  |  |

| 24 | LED0/PHY_ADR0    | O/LI/PD | LED0, Link 10Mbps On, Active Blink.<br>Hardware Bootstrap: PHY Address [0]                                                                                                                                                                                                                                                                                                                |                                          |                                                                                                                      |  |  |  |

Songshan Lake • Dongguan • Guangdong

| 25 | LED1/PHY_ADR1 O/LI/PD |   | LED1, Link 100Mbps On, Active Blink.<br>Hardware Bootstrap: PHY Address [1] |  |  |  |

|----|-----------------------|---|-----------------------------------------------------------------------------|--|--|--|

|    | MISC                  |   |                                                                             |  |  |  |

| 1  | R <sub>BIAS</sub>     | I | Bias Resistor Connection. External 2.49 kΩ 1% resistor connection to GND.   |  |  |  |

|    |                       |   |                                                                             |  |  |  |

| 30 | NC                    |   |                                                                             |  |  |  |

I: Input Signal

O: Output Signal

PWR: Power Supply

GND: Ground

EPAD: Exposed thermal PAD

PU: Pulled Up

PD: Pulled Down

LI: Latched Input during Power up or Reset

### **2** Electrical Characteristics

# 2.1 Absolute Maximum Ratings

Table2. Absolute Maximum Ratings

| Parameter                  | Cymbol         |      | Value |      | Unit | Notes                  |

|----------------------------|----------------|------|-------|------|------|------------------------|

| rarameter                  | Symbol         | Min. | Тур.  | Max. | Unit | Notes                  |

|                            | $V_{DDA\_1V}$  | -0.2 |       | 1.5  | V    | Analog supply voltage  |

| Power Supply Voltage       | $V_{DD_{-1}V}$ | -0.2 |       | 1.5  | V    | Digital supply voltage |

|                            | $V_{DDA\_3V3}$ | -0.3 |       | 3.70 | V    | Analog supply voltage  |

| 4                          | $V_{DD\_3V3}$  | -0.3 |       | 3.70 | V    | Digital supply voltage |

| Storage temperature        | $T_{STG}$      |      |       | 150  | °C   |                        |

| Lead Soldering Temperature | $T_{Lead}$     |      |       | 260  | °C   | Soldering 10 seconds   |

# 2.2 Recommended Operating Conditions

Table3. Recommended Operating Conditions

| Danamatan       | Symbol               |      | Value | ,    | Unit | Notes |

|-----------------|----------------------|------|-------|------|------|-------|

| Parameter       | Symbol               | Min. | Тур.  | Max. | Unit |       |

|                 | $V_{DDA\_1V}$        | 1.10 | 1.20  | 1.30 | V    |       |

| Complex Valtage | $V_{DD_{-1}V}$       | 1.10 | 1.20  | 1.30 | V    |       |

| Supply Voltage  | V <sub>DDA_3V3</sub> | 2.97 | 3.30  | 3.63 | V    |       |

|                 | $V_{DD\_3V3}$        | 2.97 | 3.30  | 3.63 | V    |       |

| Parameter                                 | Cymph ol          |      | Value | ,    | IIm:4 | Notes                          |

|-------------------------------------------|-------------------|------|-------|------|-------|--------------------------------|

| rarameter                                 | Symbol            | Min. | Тур.  | Max. | Unit  | Notes                          |

| Operating Junction Temperature            | $T_{JUNC}$        |      |       | 125  | °C    |                                |

| Operation temperature                     | $T_{OPR}$         | 0    | 25    | 70   | °C    |                                |

| Max. Junction Temperature                 | Tjunc             | 0    |       | 125  | °C    |                                |

| 0                                         | T                 | 0    | 25    | 70   | °C    | DAP8201M                       |

| Operation temperature                     | Topr              | -40  | 25    | 85   | °C    | DAP8201MI                      |

| Thermal resistance - junction to ambient  | $\theta_{\rm JA}$ |      | 37.8  |      | °C/W  | JEDEC with no air flow TA=25°C |

| Thermal resistance - junction to board    | $	heta_{ m JB}$   |      | 16.1  |      | °C/W  | JEDEC with no air flow         |

| Thermal resistance - junction to top case | ӨЈС-Тор           |      | 34.8  |      | °C/W  | JEDEC with no air flow         |

# 2.3 Power Consumption

Table4. Power consumption

| Condition    | MII    | RMII   | Unit |

|--------------|--------|--------|------|

| Reset        | 16.5   | 16.5   | mW   |

| Power Down   | 18.48  | 18.48  | mW   |

| Sleep Mode   | 20.13  | 20.13  | mW   |

| Active       | 147.84 | 145.2  | mW   |

| Link 10M     | 79.53  | 77.88  | mW   |

| Link 100M    | 217.47 | 201.3  | mW   |

| Traffic 10M  | 135.3  | 133.65 | mW   |

| Traffic 100M | 212.52 | 189.35 | mW   |

The power consumption is measured under room temperature with typical process DUT.

### 2.4 DC Characteristics

Table5. DC Characteristics

| Parameter                      | Cymbol            |      | Value    |      | Unit | Notes                                  |  |  |

|--------------------------------|-------------------|------|----------|------|------|----------------------------------------|--|--|

| rarameter                      | Symbol            | Min. | Тур.     | Max. | UIII | Notes                                  |  |  |

| 3.3VHigh-level input voltage   | $ m V_{IH}$       | 2.0  |          |      | V    | V <sub>DD_3</sub> v <sub>3</sub> =3.3V |  |  |

| 3.3V Low-level input voltage   | V <sub>IL</sub>   |      | \\ \\ \' | 0.8  | V    | $V_{DD_{_{_{3}V_{3}}}=3.3V}$           |  |  |

| 3.3V High-level output voltage | $V_{\mathrm{OH}}$ | 2.4  | )        |      | V    | V <sub>DD_3V3</sub> =3.3V              |  |  |

| 3.3V Low-level output voltage  | V <sub>OL</sub>   |      |          | 0.4  | V    | V <sub>DD_3V3</sub> =3.3V              |  |  |

# 2.5 Timing Characteristics

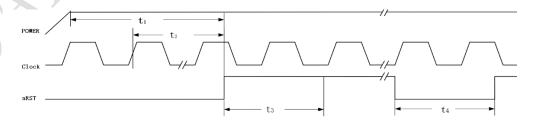

# 2.5.1 Reset Timing

Figure 1. Reset Timing

Table6. Reset Timing

| Parameter                                   | Symbol         |      | Unit |      |     |

|---------------------------------------------|----------------|------|------|------|-----|

| 1 at affecter                               | Symbol         | Min. | Тур. | Max. | Omt |

| Reset assert time after power on            | $t_1$          | 100  |      |      | ms  |

| Reset assert time after clock ready         | $t_2$          | 10   |      |      | ms  |

| Reset de-assert time after power on         | t <sub>3</sub> | 5    |      |      | ms  |

| Minimum reset pulse during normal operation | t <sub>4</sub> | 10   |      |      | ms  |

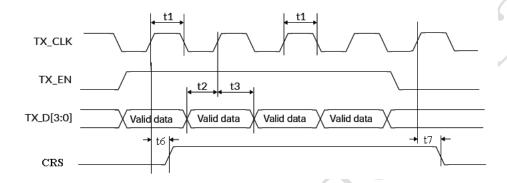

# 2.5.2 MII Interface Timing

Figure 2. 10Mbps/100Mbps MII Transmit Timing

Figure 3. 10Mbps/100Mbps MII Receive Timing

Table7. 100Mbps MII Timing

14

| Parameter                                           | Symbol |      | Value |      | Unit | Notes       |

|-----------------------------------------------------|--------|------|-------|------|------|-------------|

| 1 at afficier                                       | Symbol | Min. | Тур.  | Max. | Omt  | Notes       |

| TX_CLK high/low time                                | t1     | 14   | 20    | 26   | ns   | 100Mbps MII |

| TX_D[3:0], TX_EN data setup to TX_CLK               | t2     | 10   |       |      | ns   | mode        |

| TX_D[3:0], TX_EN data hold from TX_CLK              | t3     | 0    |       |      | ns   |             |

| RX_CLK high/low time                                | t4     | 14   | 20    | 26   | ns   |             |

| RX_CLK to RX_D[3:0], RX_DV, RX_ER delay             | t5     | 10   |       | 30   | ns   |             |

| TX_EN Sampled to CRS High                           | t6     |      |       | 40   | ns   |             |

| TX_EN Sampled to CRS Low                            | t7     |      |       | 160  | ns   |             |

| Receive Frame to CRS High                           | t8     |      |       | 130  | ns   |             |

| Receive Frame to sampled clock edge of RX_DV        | t9     |      |       | 150  | ns   |             |

| End of Receive Frame to CRS Low                     | t10    |      |       | 240  | ns   |             |

| End of Receive Frame to sampled clock edge of RX_DV | t11    | 10   |       | 120  | ns   |             |

Table8. 10Mbps MII Timing

| Parameter                                           | Symbol |          | Value    |      | Unit | Notes      |

|-----------------------------------------------------|--------|----------|----------|------|------|------------|

| 1 at affected                                       | Symbol | Min.     | Тур.     | Max. | Omt  | Tious      |

| TX_CLK high/low time                                | t1     | 140      | 200      | 260  | ns   | 10Mbps MII |

| TX_D[3:0], TX_EN data setup to TX_CLK               | t2     | 5        |          |      | ns   | mode       |

| TX_D[3:0], TX_EN data hold from TX_CLK              | t3     | 0        |          |      | ns   |            |

| RX_CLK high/low time                                | t4     | 160      | 200      | 240  | ns   |            |

| RX_CLK to RX_D[3:0], RX_DV, RX_ER delay             | t5     | 100      |          | 300  | ns   |            |

| TX_EN Sampled to CRS High                           | t6     |          | ,        | 400  | ns   |            |

| TX_EN Sampled to CRS Low                            | t7     |          |          | 2000 | ns   |            |

| Receive Frame to CRS High                           | t8     |          | )        | 2000 |      |            |

| Receive Frame to sampled clock edge of RX_DV        | t9     |          | <b>N</b> | 3200 |      |            |

| End of Receive Frame to CRS Low                     | t10    | <b>Y</b> |          | 1000 |      |            |

| End of Receive Frame to sampled clock edge of RX_DV | t11    | 10       |          | 1000 | ns   |            |

| TX_EN Sampled to CRS Low                            | t7     |          |          | 2000 | ns   |            |

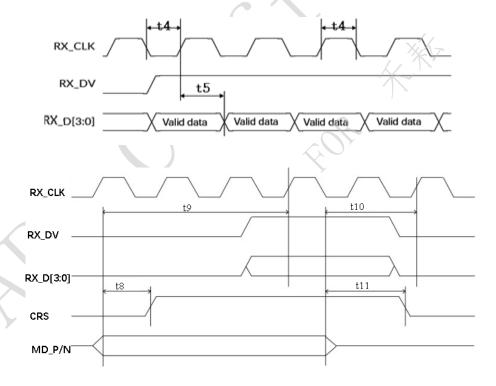

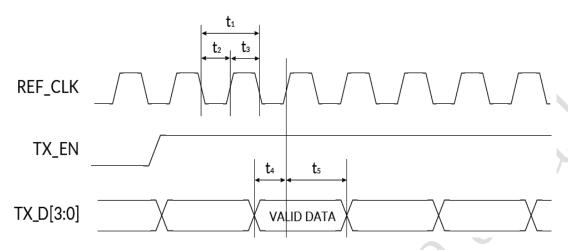

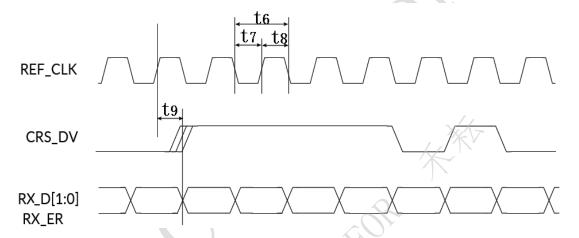

# 2.5.3 RMII Interface Timing

Figure 4. RMII Transmit Timing

Figure 5. RMII Receive Timing

Table9. RMII Timing

| Parameter                                                  | Symbol |      | Value | Unit | Notes |        |

|------------------------------------------------------------|--------|------|-------|------|-------|--------|

| 1 at affect                                                | Symbol | Min. | Тур.  | Max. | Omt   | riotes |

| REF_CLK(TX_CLK) clock period                               | t1, t6 |      | 20    |      | ns    |        |

| REFCLK(TX_CLK) clock duty cycle                            |        | 35   | 50    | 65   | %     |        |

| TX_D[1:0], TX_EN, data setup to REF_CLK(TX_CLK) rising     | t4     | 4    |       |      | ns    |        |

| TX_D[1:0], TX_EN, data hold from REF_CLK(TX_CLK) rising    | t5     | 2    |       |      | ns    |        |

| RX_D[1:0], CRS_DV output delay from REF_CLK(TX_CLK) rising | t9     | 2    |       | ·    | ns    |        |

Table 10. 10Mbps RMII Timing

| Parameter            |        |      | Value |      | Unit | Notes  |

|----------------------|--------|------|-------|------|------|--------|

| T at affected        | Symbol | Min. | Тур.  | Max. | Omi  | rotes  |

| TX_CLK high/low time | t1     | 140  | 200   | 260  | ns   | 10Mbps |

Songshan Lake • Dongguan • Guangdong

| Parameter                               |        |      | Value | Unit | Notes |       |

|-----------------------------------------|--------|------|-------|------|-------|-------|

| 1 at affected                           | Symbol | Min. | Тур.  | Max. | Omt   | Notes |

| TX_D[3:0], TX_EN data setup to TX_CLK   | t2     | 10   |       |      | ns    | MII   |

| TX_D[3:0], TX_EN data hold from TX_CLK  | t3     | 1    |       |      | ns    | mode  |

| RX_CLK high/low time                    | t4     | 160  | 200   | 240  | ns    |       |

| RX_CLK to RX_D[3:0], RX_DV, RX_ER delay | t5     | 100  |       | 300  | ns    |       |

# 2.6 Reference Clock Requirements

Table 11. Crystal Specification

| Danamatan              |      | Value Unit |      | Unit | Notes |

|------------------------|------|------------|------|------|-------|

| Parameter              | Min. | Тур.       | Max. | Unit | Notes |

| Frequency              |      | 25         |      | MHz  |       |

| Frequency<br>Stability | -50  |            | 50   | ppm  |       |

| ESR                    |      |            | 50   | Ω    |       |

| Drive Level            |      |            | 0.5  | mW   |       |

Table 12. Oscillator Specification

| Parameter                |      | Value |      | Unit | Notes                           |

|--------------------------|------|-------|------|------|---------------------------------|

| r ar ameter              | Min. | Тур.  | Max. | Unit | Notes                           |

| Frequency                |      | 25    |      | MHz  |                                 |

| Frequency<br>Stability   | -50  |       | 50   | ppm  | X/\_                            |

| Rise/Fall Time           |      |       | 6    | ns   | 10% - 90%                       |

| Cycle to Cycle<br>Jitter |      |       | 200  | ps   | short term (peak to peak value) |

| Duty Cycle               | 40   |       | 60   | %    |                                 |

| V <sub>IH</sub>          | 1.4  |       | 3.6  | V    |                                 |

| V <sub>IL</sub>          |      | )     | 0.4  | V    |                                 |

## 3 Detail Description

## 3.1 Block Diagram

Figure 6. Functional Block Diagram

## 3.2 Feature Description

### 3.2.1 WoL (Wake-on-LAN)

Wake-on-LAN provides a mechanism to detect dedicated frames and inform the connected MAC through either a register status change, WoL indication, or an interrupt flag. The connected devices (MAC) placed above the Physical Layer to operate in a low power mode until special frames are detected. Supported WoL types include: Magic Packet.

When configured for Wake-on-LAN mode, the DAP8201M(I) will check all incoming frames to identify the Magic Packet frame.

A Magic Packet frame must also meet the basic requirements for the Ethernet Frame.

The specific Magic Packet sequence consists of 16 duplications of the IEEE address of this node, with no breaks or interruptions. This sequence can be located anywhere within the packet but must be preceded by a synchronization stream. The synchronization stream is defined as 6 bytes of 0xFF.

Table 13. Magic Packet Structure

| Destination                   |  |

|-------------------------------|--|

| (6 bytes)                     |  |

|                               |  |

| Source                        |  |

| (6 bytes)                     |  |

|                               |  |

| MISC                          |  |

| $(X \text{ bytes, } X \ge 0)$ |  |

|                               |  |

| FFFFFFFFFF                    |  |

| (6 bytes)                     |  |

| (o bytes)                     |  |

| Destination*16                |  |

| (6*16 bytes)                  |  |

| (0 10 bytes)                  |  |

| MISC                          |  |

|                               |  |

| (X bytes, X >= 0)             |  |

|                               |  |

| CRC                           |  |

| (4 bytes)                     |  |

| (. 5) (65)                    |  |

EXT 0x4004, 0x4005 and 0x4006 are the 48-bit MAC address registers.

EXT 0x4000 bit2 controls the WoL mechanism.

RX\_D[1] just controls pin24 LED0 working as WoL interrupt. When the pad RX\_D1 is externally pulled up, pin24 will work as WoL interrupt.

If EXT 0x4003 bit7 is 0, the dedicated WoL interrupt is programmed to a level, otherwise, it's programmed to a pulse; either is active low. When it's programmed to a pulse, the pulse width can be programmed via EXT 0x4003 bit9:8.

WoL interrupt is also wire-and to general PHY interrupt RX\_D2\_INT when the bit6 INT\_WoL in Interrupt enable register (Basic Register 0x12) is set to 1. If the general PHY interrupt is triggered by WoL, it can be cleared by reading MII register 0x13 bit6.

#### NOTE:

When general PHY interrupt is used to monitor WoL interrupt, EXT 0x4003 bit7 should be 1, otherwise, the general PHY interrupt can't be read cleared.

Because PHY requires to receive packets from the line side, PHY cannot be powered down. If the link partner supports Energy Efficient Ethernet function, both ends can use EEE mode to save more power.

MII register 0x0 bit10 ISOLATE: When this bit is set to 1, the MII/RMII output pins are High Z. The MII/RMII inputs are ignored.

### 3.2.2 Auto-Negotiation

DAP8201M(I) supports Auto-Negotiation function which is defined in 802.3u. Auto-Negotiation function is to exchange information between two devices that share a link segment and to automatically configure both devices to take maximum advantage of their abilities.

The basic mechanism to achieve Auto-Negotiation is to pass information encapsulated within a burst of closely spaced

Songshan Lake · Dongguan · Guangdong

link integrity test pulses that individually meet the 10Base-Te Transmitter Waveform for Link Test Pulse. This burst of pulses is referred to as a Fast Link Pulse Burst.

The Auto-Negotiation function allows the devices to switch between the various operational modes in an ordered fashion, permits management to disable or enable the Auto-Negotiation function, and allows management to select a specific operational mode. The Auto-Negotiation function also provides a Parallel Detection function to allow 10Base-Te and 100Base-TX compatible devices to be recognized, even though they may not provide Auto-Negotiation.

#### 3.2.3 Auto-MDIX

The function implements crossover detection automatically for MDI/MDIX cables which easies connection process. Auto-MDIX is enabled by default and can be configured via register (register 28, page 0), bits [2:1].

### 3.2.4 Automatic Polarity Correction

The DAP8201M(I) also implements polarity auto correction when cable happens to have wrong polarity connected when working at 10Base-Te mode. DAP8201M(I) will detect the polarity of Normal Link Pulse to determine the polarity of cable.

#### 3.2.5 IEEE 802.3az-2010 EEE

The DAP8201M(I) supports IEEE 802.3az-2010(EEE: Energy Efficient Ethernet). EEE defines a negotiation method to enable link partners to decide whether EEE is supported.

Based on link utilization efficiency and EEE protocol, the transitions would work in different mode. When no packets are being transmitted, DAP8201M(I) would work in Low Power Idle mode to save power. As soon as packets to be transmitted, DAP8201M(I) returns to normal mode, and this doesn't impact the link status and dropping frames.

#### 3.2.6 UTP Ethernet

DAP8201M(I) supports the 100Base-TX and 10Base-Te standard as defined by the IEEE 802.3 standard.

In 100M mode, the PHY will use two pairs MDI channels for communication. The communicated data are encoded/decoded in 4B/5B.

In 10M mode, the PHY will also use two pairs MDI channels for communication. The communicated data are encoded/decoded in Manchester.

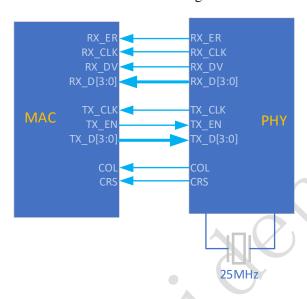

### 3.2.7 MII Interface

The Media Independent Interface is a synchronous 4-bit wide nibble data interface that connects the PHY to the MAC in 100Base-TX and 10Base-Te modes. The MII is compliant with IEEE 802.3-2002 clause 22.

Additionally, the MII interface includes the carrier sense signal (CRS), as well as a collision detect signal (COL). The CRS signal asserts to indicate the reception or transmission of data. The COL signal asserts as an indication of a collision which can occur during Half-Duplex mode when both transmit and receive operations occur simultaneously.

Transmission: The MAC asserts the TX EN signal firstly, then changes byte data into 4-bit and transmits them to the

PHY via TX\_D[3:0]. The PHY will sample TX\_D[3:0] synchronously with TX\_CLK – the transmit clock signal supplied by the PHY.

Reception: The PHY asserts the RXDV signal firstly. It transmits the received data RX\_D[3:0] clocked by RX\_CLK. CRS and COL signals are used for collision detection and handling.

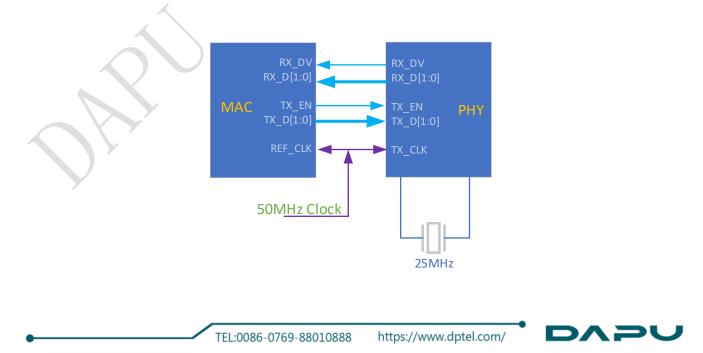

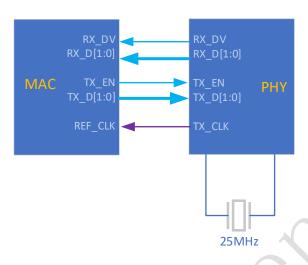

#### 3.2.8 RMII Interface

The DAP8201M(I) incorporates the Reduced Media Independent Interface (RMII) as specified in the RMII specification from the RMII consortium. The purpose of this interface is to provide a reduced pin count alternative to the IEEE 802.3u MII as specified in Clause 22. Architecturally, the RMII specification provides an additional reconciliation layer on either side of the MII, but it can be implemented in the absence of an MII.

1. RMII1 mode: This is fully conforming to RMII standard. DAP8201M(I) can use clock from TX\_CLK as reference clock for internal PLL. Configure bit 6 of extended register (address 0x50) to 1 to enable: not need 25MHz crystal at XI/XO.

2. RMII2 mode: TX CLK will output 50MHz to MAC, this can save one 50MHz clock.

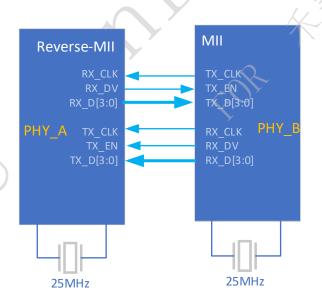

#### 3.2.9 Reverse MII Interface

DAP8201M(I) supports reverse media independent interface. The only difference is the direction of  $TX\_CLK$  and  $RX\_CLK$ . For MII,  $TX\_CLK$  and  $RX\_CLK$  are output; for Reverse MII,  $TX\_CLK$  and  $RX\_CLK$  are input.

In Reverse MII mode, two PHYs are connected back-to-back via the MII interface to realize a repeater function on the physical layer.

### 3.2.10 Loopback Mode

There are several options for loopback mode that test and verify various functional blocks within the PHY. Enabling loopback mode allows in-circuit testing of the digital and analog data paths. Generally, the DAP8201M(I) may be configured to 3 loopback modes.

TEL:0086-0769-88010888 https://www.dptel.com/

| Loopback Mode     | Description                                                                                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Loopback | When BMCR register field Loopback is set to "1", data sent through DAC to ADC directly.                                                                                                                                                |

| External Loopback | An external loopback stub allows testing the complete data path without the need of a link partner. In this case it seems the data send through MII/RMII TX interface with be forwarded to MII/RMII RX interface through MDI interface |

| Remote Loopback   | When Remote_loopback bit of extended register(0x4000) is set to "1", data transmitted from MII/RMII tx interface will route back to MII/RMII rx interface. This checks if MII/RMII works correctly for remote link.                    |

### 3.2.11 Hardware Bootstrap Configuration

The MII/RMII mode, and PHY address can be set by hardware. These configurations are setup through dedicated IO pin with external pullup/pulldown resistor. When power on reset is de-asserted, the hardware circuit will sample values on these dedicated IO pin.

Function Pin Pin Name **Description** Number Pin12 Media Mode Hardware MII **Bootstrap** Reverse MII 0 1 RMII2(TX\_CLK outputs 50MHz 0 for Media Reference clock by default) RX\_DV/MII\_M 8 Mode Select RMII1(TX\_CLK inputs 50MHz 12 RX\_D3/TX\_CLK\_CTR Reference clock 0: pin24 works as LED0 LED/WOL 10 RX\_D1/WoL PHY Address Pin25 Pin24 00000 0 0 PHY 0 00001 Address LED0/PHY\_ADR0 24 0 1 00010 1 00011 25 LED1/PHY\_ADR1

Table 14. Hardware Bootstrap

#### 3.2.12 Reset

There are two types of reset operation: Hardware Reset and Software Reset.

Hardware Reset: A hardware reset is implemented by asserting the nRST pin with low level: at least 10ms. All registers will be reset to default values and the hardware configuration will be re-latched.

Software Reset: A software reset is accomplished by writing BMC-C[15] Reset register to 1. All registers will be reset to default values and the hardware configuration will not be re-latched. Software need wait 100us to start other SMI operation.

### 3.2.13 Power Supply

DAP8201M(I) integrates the internal linear regulator and needs to supply a single 3.3V power source.

TEL:0086-0769-88010888

https://www.dptel.com/

## 4 Registers

# 4.1 Register mapping

The DAP8201M(I) includes 2 register groups.

| - | Register Group  | Description                                        |

|---|-----------------|----------------------------------------------------|

| 1 | Basic Register  | Basic Register based on IEEE802.3                  |

| 2 | Extend Register | Extend Register based on Extended Register Mapping |

Note: Basic Register is same to MII Register.

# 4.2 Register Access Types

| Type | Description                                                                                                                                                                                            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RW   | Read and write                                                                                                                                                                                         |

| RO   | Read only.                                                                                                                                                                                             |

| SC   | Self-clear.  If default value is '0' ('1'), writing a '1' ('0') to this register field causes the function to be activated immediately, and then the field will be automatically cleared to '0' ('1'). |

| RC   | Read clear.                                                                                                                                                                                            |

| SWC  | Software reset to 0.                                                                                                                                                                                   |

| SWS  | Software reset to 1.                                                                                                                                                                                   |

| PS   | Default value depends on power on strapping.                                                                                                                                                           |

| LH   | Latch high.                                                                                                                                                                                            |

| LL   | Latch Low.                                                                                                                                                                                             |

# 4.3 Basic Register

| T4   | Address |               | Function                              |

|------|---------|---------------|---------------------------------------|

| Item | Offset  | Register Name | Description                           |

| 1    | 0x0     | BMCR          | Basic Mode Control                    |

| 2    | 0x1     | BMSR          | Basic Mode Status                     |

| 3    | 0x2     | PHYID1        | PHY Identifier Register #1            |

| 4    | 0x3     | PHYID2        | PHY Identifier Register #2            |

| 5    | 0x4     | ANAR          | Auto-Negotiation Advertisement        |

| 6    | 0x5     | ANLPA         | Auto-Negotiation Link Partner Ability |

| 7    | 0x6     | ANE           | Auto-Negotiate Expansion              |

| 8    | 0x7     | ANNPT         | Auto-Negotiate Next Page Transmit     |

| 9    | 0x8     | ANNPR         | Auto-Negotiate Next Page Receive      |

| 10   | 0xA     | MSSR          | Master-Slave Status Register          |

| 11   | 0xD     | MMD_AC        | MMD Access Control                    |

| 12   | 0xE     | MMD_AADA      | MMD Access Address and Data           |

Songshan Lake • Dongguan • Guangdong

| 13 | 0x10 | PHYCR    | PHY Control Register               |

|----|------|----------|------------------------------------|

| 14 | 0x11 | PHYSR    | PHY Status Register                |

| 15 | 0x12 | INTCR    | Interrupt Control Register         |

| 16 | 0x13 | INTSR    | Interrupt Status Register          |

| 17 | 0x14 | SPCR     | Speed Configuration Register       |

| 18 | 0x15 | RECR     | Receiver Error Counter Register    |

| 19 | 0x1E | EXT_ADD  | Extended Register Address Register |

| 20 | 0x1F | EXT_DATA | Extended Register Data Register    |

## 4.3.1BMCR(Basic Mode Control Register, Address: Register 0x0)

### Table 15. BMCR

| Bit      | Name     | Default | Description                                                                  | Access  |

|----------|----------|---------|------------------------------------------------------------------------------|---------|

| 15       | Reset    | 0       | Reset.                                                                       | RW, SC  |

|          |          |         | 1: PHY reset                                                                 |         |

|          |          |         | 0: Normal operation                                                          |         |

|          |          |         | Software Reset. Writing a '1' to this bit to reset the PHY states machine.   |         |

|          |          |         | Register 0 (BMCR) and register 1 (BMSR) will return to default values once   |         |

|          |          |         | the reset operation is done.                                                 |         |

| 14       | Loopback | 0       | Internal Loopback Mode.                                                      | RW      |

|          |          |         | 1: Enable internal loopback mode                                             |         |

|          |          |         | 0: Disable internal loopback mode                                            |         |

| 13       | Speed[0] | 1       | Speed Select Bit                                                             | RW      |

|          |          |         | Speed [1:0]:                                                                 |         |

|          |          |         | 11: Reserved                                                                 |         |

|          |          |         | 10: Reserved                                                                 |         |

|          |          |         | 01:100Mbps                                                                   |         |

|          |          |         | 0: 10Mbps                                                                    |         |

|          |          |         | After completing auto negotiation, this bit will reflect the speed status.   |         |

|          |          |         | 1:100Base-T                                                                  |         |

|          |          |         | 0:10Base-Te                                                                  |         |

| 12       | AN E     | 1       | Auto-Negotiation Enable.                                                     | RW      |

|          |          |         | 1: Enable Auto-Negotiation                                                   |         |

|          |          | 4       | 0: Disable Auto-Negotiation                                                  |         |

| 11       | PWD      | . 0     | Power Down.                                                                  | RW      |

|          |          |         | 1: Power down (only Management Interface and logic are active; link is       |         |

|          |          |         | down)                                                                        |         |

|          |          |         | 0: Normal Operation                                                          |         |

| 10       | Isolate  | 0       | Isolate.                                                                     | RW      |

|          |          |         | 1: Isolate                                                                   |         |

|          |          |         | 0: Normal Operation                                                          |         |

|          |          |         | MII interface is isolated; the serial management interface (MDC,             |         |

|          |          |         | MDIO) is still active. When this bit is asserted, the PHY ignores TX D[3:0], |         |

|          |          |         | and TXCTL inputs, and presents a high impedance on RXC, RXCTL,               |         |

|          |          |         | RX D[3:0]                                                                    |         |

| 9        | RS_AN    | 0       | Restart Auto-Negotiation.                                                    | RW/SC   |

|          |          |         | 1: Restart Auto-Negotiation                                                  | 10,7,50 |

|          |          |         | 0: Normal operation                                                          |         |

| 8        | Duplex   | 1       | duplex mode set                                                              | RW      |

|          | Dapiex   | 1       | if auto-negotiation is disabled (register bit 12=0).                         | 1011    |

|          |          |         | 1: Full duplex                                                               |         |

|          |          |         | 0: Half duplex                                                               |         |

| <u> </u> |          | L       | v. Hull duples                                                               |         |

Songshan Lake • Dongguan • Guangdong

|     |                   |   | After completing auto-negotiation, this bit will reflect the duplex status.  1: Full duplex  0: Half duplex |    |

|-----|-------------------|---|-------------------------------------------------------------------------------------------------------------|----|

| 7   | Collision<br>Test | 0 | Collision Test. 1: Enable Collision Test 0: Normal Operation                                                | RW |

| 6   | Speed [1]         | 0 | Speed Select Bit 1 Refer to bit 0[13].                                                                      | RW |

| 5:0 | Reserved          | - | Reserved                                                                                                    | -  |

# 4.3.2 BMSR (Basic Mode Status Register, Address: Register 0x1)

Table16. BMSR

| Bit  | Name         | Default | Description                                                         | Access |

|------|--------------|---------|---------------------------------------------------------------------|--------|

| 15   | 100Base-T4   | 0       | 100Base-T4 Capability.                                              | RO     |

|      |              |         | 1: Enable 100Base-T4 support                                        |        |

|      |              |         | 0: Suppress 100Base-T4 support                                      |        |

| 14   | 100Base-TX_F | 1       | 100Base-TX Full Duplex Capability.                                  | RO     |

|      |              |         | 1= full-duplex 100Base-TX can be performed by PHY.                  |        |

|      |              |         | 0=full-duplex 100Base-TX cannot be performed by PHY.                |        |

| 13   | 100Base-TX_H | 1       | 100Base-TX Half Duplex Capability.                                  | RO     |

|      |              |         | 1= half-duplex 100Base-TX can be performed by PHY.                  |        |

|      |              |         | 0= half-duplex 100Base-TX cannot be performed by PHY.               |        |

| 12   | 10Mbps F     | 1       | 10Mbps Full Duplex Capability.                                      | RO     |

|      | 1 -          |         | 1= full-duplex 10Base-Te can be performed by PHY.                   |        |

|      |              |         | 0=full-duplex 10Base-Te cannot be performed by PHY.                 |        |

| 11   | 10Mbps H     | 1       | 10Mbps half -duplex Capability.                                     | RO     |

|      | 1 =          |         | 1= half-duplex 10Base-Te can be performed by PHY.                   |        |

|      |              |         | 0= half-duplex 10Base-Te cannot be performed by PHY.                |        |

| 10:9 | Reserved     | 00      | Reserved                                                            | RO     |

| 8    | Ext Status   | 1       | Extended status register in 0x0F                                    | RO     |

|      | _            |         | 1: Supported extended status register                               |        |

|      |              |         | 0: Not supported extended status register                           |        |

| 7    | Transmit_MII | 0       | 1: PHY able to transmit from MII regardless of whether the PHY      | RO     |

|      | _            |         | has detected that a valid link has been established.                |        |

|      | <b>A</b>     |         | 0: PHY able to transmit from MII only when the PHY has              |        |

|      |              |         | detected that a valid link has been established.                    |        |

| 6    | MF PS        | 1       | 1: The PHY will accept management frames with preamble              | RO     |

|      |              |         | suppressed.                                                         |        |

|      |              |         | 0: The PHY will not accept management frames with preamble          |        |

|      |              |         | suppressed.                                                         |        |

|      |              |         | A minimum of 32 preamble bits are required: the first               |        |

|      |              |         | management interface read/write transaction after reset. One idle   |        |

|      |              |         | bit is required between any two management transactions as per      |        |

|      |              |         | IEEE 802.3u specifications.                                         |        |

| 5    | AN_C         | 0       | Auto-Negotiation Complete.                                          | RO     |

|      |              |         | 1=Auto-Negotiation process is complete.                             |        |

|      |              |         | 0=Auto-Negotiation process is not complete.                         |        |

| 4    | Remote Fault | 0       | Remote Fault.                                                       | RC     |

|      |              |         | 1=Remote fault condition is detected (cleared on read or by reset). |        |

|      |              |         | 0=Remote fault condition is not detected.                           |        |

| 3    | AN A         | 1       | Auto-Negotiation Ability.                                           | RO     |

|      |              | 1       |                                                                     |        |

Songshan Lake • Dongguan • Guangdong

|   |                |   | 1=Auto-Negotiation can be performed by PHY                         |    |

|---|----------------|---|--------------------------------------------------------------------|----|

|   |                |   | 0=Auto-Negotiation cannot be performed by PHY                      |    |

| 2 | Link Status    | 0 | Link Status                                                        | RO |

|   |                |   | 1: Linked                                                          |    |

|   |                |   | 0: Not Linked                                                      |    |

|   |                |   | This bit indicates whether the link was lost since the last read.: |    |

|   |                |   | the current link status, read this register twice.                 |    |

| 1 | Jabber Detect  | 0 | Jabber Detect                                                      | RO |

|   |                |   | 1: Jabber condition detected                                       |    |

|   |                |   | 0: No Jabber detected                                              |    |

| 0 | Ext_Capability | 1 | 1: Extended register capable (permanently=1)                       | RO |

|   |                |   | 0: Not extended register capable                                   |    |

|   |                |   | To indicate whether support EXTs, to access from address register  |    |

|   |                |   | 0x1E and data register 0x1F.                                       |    |

### 4.3.3 PHYID1 (PHY Identifier Register #1, Address: Register 0x2)

### Table17. PHYID1

| Bit  | Name      | Default | Description               | Access |

|------|-----------|---------|---------------------------|--------|

| 15:0 | PHYID_LSB |         | PHY Identifier Bit [18:3] | RO     |

## 4.3.4 PHYID2 (PHY Identifier Register #2, Address: Register 0x3)

### Table18. PHYID2

| Bit   | Name      | Default | Description                | Access |

|-------|-----------|---------|----------------------------|--------|

| 15:10 | PHYID_MSB |         | PHY Identifier Bit [24:19] | RO     |

| 9:4   | Model     | 01 0010 | Manufacture's Model Number | RO     |

|       | Number    |         |                            |        |

| 3:0   | Revision  | 1000    | Revision Number            | RO     |

|       | Number    |         |                            |        |

## 4.3.5 ANAR (Auto-Negotiation Advertising, Address: Register 0x4)

This register contains the advertised abilities of this device as they will be transmitted to its link partner during autonegotiation.

Table 19. ANAR

| Bit | Name          | Default | Description                                                    | Access |

|-----|---------------|---------|----------------------------------------------------------------|--------|

| 15  | Next Page*    | 0       | Next Page Bit.                                                 | RW     |

|     |               |         | 1: Advertise                                                   |        |

|     |               |         | 0: Not advertised                                              |        |

| 14  | Reserved      | 0       | Reserved                                                       | RO     |

| 13  | Remote Fault  | 0       | Remote Fault                                                   | RW     |

|     |               |         | 1: Set Remote Fault bit                                        |        |

|     |               |         | 0: No Remote Fault bit                                         |        |

| 12  | Ext_Next_Page | 1       | Extended next page enable control bit                          | RW     |

|     |               |         | 1: Local device supports transmission of extended next pages   |        |

|     |               |         | 0: Local device does not support transmission of extended next |        |

DAPU

Songshan Lake • Dongguan • Guangdong

|     |                |       | pages.                                                |    |

|-----|----------------|-------|-------------------------------------------------------|----|

| 11  | Asymmetric     | 1     | Asymmetric PAUSE                                      | RW |

|     | PAUSE*         |       | 1: Advertise asymmetric pause support                 |    |

|     |                |       | 0: No support of asymmetric pause                     |    |

| 10  | Pause*         | 1     | 1: MAC PAUSE implemented                              | RW |

|     |                |       | 0: MAC PAUSE not implemented                          |    |

| 9   | 100Base-T4     | 0     | 1: 100Base-T4 is supported by local node              | RO |

|     |                |       | 0: 100Base-T4 not supported by local node             |    |

| 8   | 100Base-TX_F*  | 1     | 1: 100Base-TX full duplex is supported by local node  | RW |

|     |                |       | 0: 100Base-TX full duplex not supported by local node |    |

| 7   | 100Base-TX_H*  | 1     | 1: 100Base-TX half duplex is supported by local node  | RW |

|     |                |       | 0: 100Base-TX half duplex not supported by local node |    |

| 6   | 10Base-Te-F*   | 1     | 1: 10Base-Te full duplex supported by local node      | RW |

|     |                |       | 0: 10Base-Te full duplex not supported by local node  |    |

| 5   | 10Base-Te H*   | 1     | 1: 10Base-Te half duplex is supported by local node   | RW |

|     |                |       | 0: 10Base-Te half duplex not supported by local node  |    |

| 4:0 | Selector Field | 00001 | Selector Field mode.                                  | RO |

|     |                |       | 00001: IEEE 802.3                                     |    |

<sup>\*:</sup> This bit is updated immediately after the writing operation; However, the configuration does not take effect until any of the following occurs:

- Software reset is asserted by writing register 0x0 bit[15]

- Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]

- The port is switched from power down to normal operation by writing register 0x0 bit[11]

- · Link goes down

# 4.3.6 ANLPA (Auto-Negotiation Link Partner Ability, Address: Register 0x5)

This register contains the advertised abilities of the Link Partner as received during auto-negotiation. The content changes after a successful auto-negotiation if Next-pages are supported.

Table20. ANLPA

| Bit | Name         | Default | Description                                                       | Access |

|-----|--------------|---------|-------------------------------------------------------------------|--------|

| 15  | Next Page    | 0       | Next Page Indication.                                             | RO     |

|     |              |         | 0: Transmitting the primary capability datapage                   |        |

|     |              |         | 1: Transmitting the protocol specific data page                   |        |