# INS6310A —1:10 Ultra-Low Additive Jitter **Differential Clock Buffer**

#### **FEATURES**

- Two banks with 5 differential outputs each

- LVPECL, LVDS, HCSL or Hi-Z (selectable per bank)

- LVPECL additive jitter with clock source at 122.88MHz

- 40 fs RMS (10KHz to 1MHz)

- 80 fs RMS (12KHz to 20MHz)

- 3:1 Input Multiplexer

- Two universal inputs operate up to 2.5GHz and accept LVPECL, LVDS, CML, SSTL, HSTL, HCSL or single-ended clocks

- One crystal input accepts 10 to 40MHz crystal or single-ended clock

- High PSRR: -65/-76dBc (LVPECL/LVDS) at 156.25MHz

- LVCMOS output with synchronous enable input

- Pin-Controlled configuration

- $V_{DD}$  core supply:  $3.3V \pm 5\%$

- 3 independent  $V_{DDO}$  output supplies:  $3.3V/2.5V \pm 5\%$

- Industrial temperature range: -40°C to +85°C

- Package: QFN48(7.0mm\*7.0mm\*0.75mm)

# **APPLICATIONS**

- High speed Clock distribution and level translation

- Wireless BBU, RRU and Wired Communication

- Servers, Computing, PCI Express (PCIe)

- Switches, Routers, Line Cards, Timing Cards

#### GENERAL DESCRIPTIONS

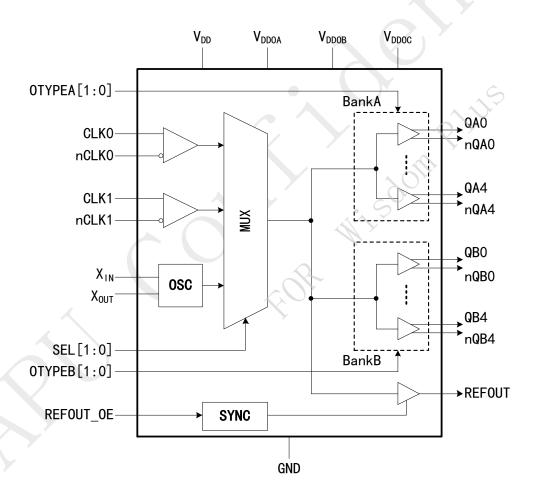

The INS6310A is a high performance, versatility 10-output differential fanout buffer intended for high-frequency, lowjitter clock/data distribution and level translation. The input clock can be selected from two universal inputs or one crystal input. The selected input clock is distributed to two banks of 5 differential outputs and one LVCMOS output. Both differential output banks can be independently configured as LVPECL, LVDS, or HCSL drivers, or disabled. The LVCMOS output has a synchronous enable input for runt-pulse-free operation when enabled or disabled. The INS6310A operates from a 3.3V core supply and 3 independent 3.3V/2.5V output supplies.

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

2

3

4

5

6

7

8

9

11

nQA3 10

QA2

Version: 1.2 **DAPU** Confidential Page: 1 / 21 35 nOB0

34 QB1

33 nQB1

32

31

30 nQB2

29 VDDOB

28 OB3

26

QB2

nQB3 27

**EPAD**

# **Table of Amendment**

| Version | Revised Content                                                                 | Draft    | Revised Date |

|---------|---------------------------------------------------------------------------------|----------|--------------|

| V1.0    | Chinese Version                                                                 |          | 2021.11.29   |

| V1.1    | English Version. Change V <sub>DDOX</sub> maximum Voltage from 3.465V to 3.45V. |          | 2022.02.08   |

| V1.2    | Error Correction: nQB* QB* pin swap in Pinouts diagram on Page 1 and Page 5     |          | 2022.06.23   |

|         |                                                                                 |          |              |

|         |                                                                                 |          |              |

|         |                                                                                 |          | >            |

|         |                                                                                 | 0        |              |

|         | • (                                                                             | <b>Y</b> | 35           |

|         | C                                                                               | 8        |              |

|         |                                                                                 | 70111    |              |

|         |                                                                                 |          |              |

|         |                                                                                 |          |              |

|         | E OF                                                                            |          |              |

| 4       | ,                                                                               |          |              |

# **INS6310A**

# Table of Contents

| 1 | GENERAL DESCRIPTION        | 4 |

|---|----------------------------|---|

| 2 | FUNCTIONAL BLOCK DIAGRAM   | ⊿ |

|   | PINOUTS                    |   |

|   | ELECTRICAL CHARACTERISTICS |   |

|   | FUNCTION DESCRIPTION       |   |

|   | ENVIRONMENT                |   |

|   | PACK AGE OUTLINE           |   |

Version: <u>1.2</u>

# 1 GENERAL DESCRIPTION

The INS6310A is a 2.5-GHz, 10-output differential fanout buffer intended for high-frequency, low-jitter clock/data distribution and level translation. The input clock can be selected from two universal inputs or one crystal input. The selected input clock is distributed to two banks of 5 differential outputs and one LVCMOS output. Both differential output banks can be independently configured as LVPECL, LVDS, or HCSL drivers, or disabled. The LVCMOS output has a synchronous enable input for runt-pulse-free operation when enabled or disabled. The INS6310A operates from a 3.3V core supply and 3 independent 3.3V/2.5V output supplies.

The INS6310A provides high performance, versatility, and power efficiency, making it ideal for replacing fixed-output buffer devices while increasing timing margin in the system.

The INS6310A does not have power supply sequencing requirements between the core and output supply domains.

# 2 FUNCTIONAL BLOCK DIAGRAM

Figure 1. Block Diagram

Version: 1.2 DAPU Confidential Page: 4/21

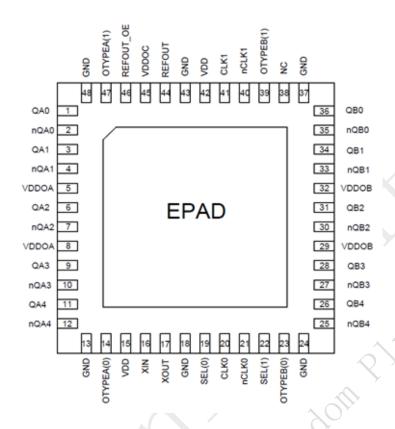

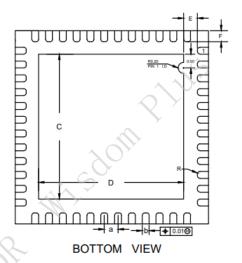

# 3 PINOUTS

Figure 2. Pinouts Diagram

Table 1. Pin Definition

|                           | Tuote 1. I in Bernmuon |      |                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|---------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PIN No.                   | PIN Name               | TYPE | DESCRIPTIONS                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 1,2                       | QA0,nQA0               | OUT  | Bank A Differential clock output 0                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 3,4                       | QA1,nQA1               | OUT  | Bank A Differential clock output 1                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 5,8                       | $V_{ m DDOA}$          | PWR  | Power supply for Bank A output buffers. V <sub>DDOA</sub> can operate from 3.3V or 2.5V. The V <sub>DDOA</sub> pins are internally tied together. Bypass with a 0.1uF low-ESR capacitor placed very close to each V <sub>DDO</sub> pin. |  |  |  |  |  |  |  |

| 6,7                       | QA2,nQA2               | OUT  | Bank A Differential clock output 2                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 9,10                      | QA3,nQA3               | OUT  | Bank A Differential clock output 3                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 11,12                     | QA4,nQA4               | OUT  | Bank A Differential clock output 4                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 13, 18, 24,<br>37, 43, 48 | GND                    | GND  | Ground                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 14,47                     | OTYPEA[0]<br>OTYPEA[1] | IN   | Bank A Outputs selection pins. Pull down internally.                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 15,42                     | $ m V_{DD}$            | PWR  | Power supply for core and input<br>buffer blocks. The VDD supply<br>operates from 3.3V. Bypass with a<br>0.1uF low-ESR capacitor placed very<br>close to each VDD pin.                                                                  |  |  |  |  |  |  |  |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 5/21

| PIN No. | PIN Name               | TYPE  | DESCRIPTIONS                                                                                                                                                                                                                            |

|---------|------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | $X_{ m IN}$            | IN    | Input for crystal. Can also be driven by a XO, TCXO, or other external single-ended clock.                                                                                                                                              |

| 17      | $X_{OUT}$              | OUT   | Output for crystal. Leave $X_{OUT}$ floating if $X_{IN}$ is driven by a single-ended clock.                                                                                                                                             |

| 19,22   | SEL[0]<br>SEL[1]       | IN    | Clock input selection pins. Pull down internally.                                                                                                                                                                                       |

| 20,21   | CLK0,nCLK0             | IN    | Universal clock input 0 (differential/single-ended).                                                                                                                                                                                    |

| 23,39   | OTYPEB[0]<br>OTYPEB[1] | IN    | Bank A Outputs selection pins. Pull down internally.                                                                                                                                                                                    |

| 25,26   | nQB4,QB4               | OUT   | Bank B Differential clock output 4                                                                                                                                                                                                      |

| 27,28   | nQB3,QB3               | OUT   | Bank B Differential clock output 3                                                                                                                                                                                                      |

| 29,32   | $ m V_{DDOB}$          | PWR   | Power supply for Bank A output buffers. V <sub>DDOA</sub> can operate from 3.3V or 2.5V. The V <sub>DDOA</sub> pins are internally tied together. Bypass with a 0.1uF low-ESR capacitor placed very close to each V <sub>DDO</sub> pin. |

| 30,31   | nQB2,QB2               | OUT   | Bank B Differential clock output 2                                                                                                                                                                                                      |

| 33,34   | nQB1,QB1               | OUT   | Bank B Differential clock output 1                                                                                                                                                                                                      |

| 35,36   | nQB0,QB0               | OUT   | Bank B Differential clock output 0                                                                                                                                                                                                      |

| 38      | NC                     | C - ^ | Not connected internally. Pin may be floated or grounded.                                                                                                                                                                               |

| 40,41   | nCLK1,CLK1             | IN    | Universal clock input 1 (differential/single-ended).                                                                                                                                                                                    |

| 44      | REFOUT                 | OUT   | LVCMOS reference output. Enable output by pulling REFOUT_OE pin high.                                                                                                                                                                   |

| 45      | V <sub>DDOC</sub>      | PWR   | Power supply for Bank A output buffers. $V_{DDOA}$ can operate from 3.3V or 2.5V. The $V_{DDOA}$ pins are internally tied together. Bypass with a 0.1uF low-ESR capacitor placed very close to each $V_{DDO}$ pin.                      |

| 46      | REFOUT_OE              | IN    | REFOUT enable input. Enable signal is internally synchronized to select clock input. Pull down internally.                                                                                                                              |

|         | EPAD                   |       | Connect to the PCB ground plane for heat dissipation.                                                                                                                                                                                   |

# 4 ELECTRICAL CHARACTERISTICS

## Table 2. Absolute Maximum Ratings

Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters Symbol | Value | Unit |

|-------------------|-------|------|

|-------------------|-------|------|

TEL:0086-0769-88010888 https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 6/21

| Power Supply Voltage                        | V <sub>DD</sub><br>V <sub>DDOA</sub><br>V <sub>DDOB</sub><br>V <sub>DDOC</sub> | -0.3~3.6                  | V    |

|---------------------------------------------|--------------------------------------------------------------------------------|---------------------------|------|

| Input Voltage                               | $V_{IN}$                                                                       | -0.3~V <sub>DD</sub> +0.3 | V    |

| Storage Temperature Range                   | $T_{STG}$                                                                      | -65~150                   | °C   |

| Junction Temperature                        | $T_{\rm J}$                                                                    | 150                       | °C   |

| Thermal resistance from Junction to Ambient | $\theta_{\mathrm{JA}}$                                                         | 28.5                      | °C/W |

Table 3. Recommended Parameters

| Daman ataua            | C b - 1                   | Value |      | TT\$4 | Notes |                                                        |  |

|------------------------|---------------------------|-------|------|-------|-------|--------------------------------------------------------|--|

| Parameters             | Symbol                    | Min.  | Тур. | Max.  | Unit  | Notes                                                  |  |

| Core Supply<br>Voltage | $V_{ m DD}$               | 3.15  | 3.3  | 3.45  | V     |                                                        |  |

| Output                 | $V_{\mathrm{DDOX}^{(1)}}$ | 3.135 | 3.3  | 3.45  | V     |                                                        |  |

| Supply<br>Voltage      | V DDOX'                   | 2.375 | 2.5  | 2.625 | V     |                                                        |  |

|                        | Iven sone                 |       | 24   | 31    | mA    | All Outputs Disabled. Clock input 0 or 1 Selected.     |  |

|                        | I <sub>VDD_CORE</sub>     |       | 23   | 30    | mA    | All Outputs Disabled. Xin Selected.                    |  |

| Core Supply            | I <sub>VDD_LVDS</sub>     |       | 50   | 75    | mA    | Additive Core Supply Current, Per LVDS Bank Enabled    |  |

| Current                | I <sub>VDD_LVPECL</sub>   |       | 20   | 26    | mA    | Additive Core Supply Current, Per LVPECL Bank Enabled  |  |

|                        | I <sub>VDD_HCSL</sub>     |       | 32   | 42    | mA    | Additive Core Supply Current, Per<br>HSCL Bank Enabled |  |

|                        | I <sub>VDD_LVCMOS</sub>   |       | 4    | 5.2   | mA    | Additive Core Supply Current, Per LVCMOS Bank Enabled  |  |

|                        | I <sub>VDDO_LVDS</sub>    |       | 24   | 31    | mA    | Additive Out Supply Current, Per LVDS Bank Enabled     |  |

| Output                 | I <sub>VDDO_LVPECL</sub>  |       | 230  | 299   | mA    | Additive Out Supply Current, Per LVPECL Bank Enabled   |  |

| Supply<br>Current      | I <sub>VDDO_HCSL</sub>    |       | 72   | 94    | mA    | Additive Out Supply Current, Per HSCL Bank Enabled     |  |

|                        | I <sub>VDDO_LVCMOS</sub>  |       | 9    | 12    | mA    | Additive Out Supply Current, Per LVCMOS Bank Enabled   |  |

| Ambient<br>Temperature | T <sub>A</sub>            | -40   |      | 85    | °C    |                                                        |  |

<sup>\* (1)</sup> DDOX will represent  $_{DDOA}/_{DDOB}/_{DDOC}$  in general when no distinction is needed

Table 4. Control Signals input Characteristics

$Test \ Condition: \ -40^{\circ}C \leq T_{A} \leq 85^{\circ}C, 3.15V \leq V_{DD} \leq 3.45V, 2.375V \leq V_{DDOX} \leq 2.625 \ or \ 3.135V \leq V_{DDOX} \leq 3.45V, 2.375V \leq V_{DDOX} \leq 3.$

| Domonostores                                                 | Ch al       |      | Value | TT24 | Notes |       |  |  |  |

|--------------------------------------------------------------|-------------|------|-------|------|-------|-------|--|--|--|

| Parameters                                                   | Symbol      | Min. | Тур.  | Max. | Unit  | Notes |  |  |  |

| Control Signals (OTYPEA[0:1],OTYPEB[0:1],SEL[0:1],REFOUT_OE) |             |      |       |      |       |       |  |  |  |

| High Level Input                                             | $ m I_{IH}$ |      |       | 50   | uA    |       |  |  |  |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 7/21

| Current                    |                   |     |     |          |    |  |

|----------------------------|-------------------|-----|-----|----------|----|--|

| Low Level Input<br>Current | $I_{\rm IL}$      | -5  | 0.1 | 5        | uA |  |

| Input High Voltage         | $V_{\mathrm{IH}}$ | 1.6 |     | $V_{DD}$ | V  |  |

| Input Low Voltage          | $V_{IL}$          | 0   |     | 0.4      | V  |  |

## Table 5. CLKx/nCLKx<sup>(2)</sup>

Test Condition: -40°C $\leq$ TA $\leq$ 85°C,3.15V $\leq$ V<sub>DD</sub> $\leq$ 3.45V,2.375V $\leq$ V<sub>DDOX</sub> $\leq$ 2.625 or 3.135V $\leq$ V<sub>DDOX</sub> $\leq$ 3.45, CLK driven differentially, input slew rate  $\geq$  3V/ns

| D                                            | Gl 1               | Value      |          |                      | TT . *4 | Nodes                                                                                                                                           |  |

|----------------------------------------------|--------------------|------------|----------|----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameters                                   | Symbol             | Min.       | Тур.     | Max.                 | Unit    | Notes                                                                                                                                           |  |

| CLKx Single-Ended Inp                        | ut Clock Spec      | ifications |          |                      | A       |                                                                                                                                                 |  |

| Single-Ended Input<br>High Voltage           | $V_{IH}$           |            |          | $V_{DD}$             | V       | CI Vv duivan single                                                                                                                             |  |

| Single-Ended Input<br>Low Voltage            | $V_{\mathrm{IL}}$  | 0          |          |                      | V       | CLKx driven single-<br>ended (AC or DC<br>coupled), nCLKx AC                                                                                    |  |

| Single-Ended Input<br>Voltage Swing(P2P)     | $V_{I\_SE}^{(3)}$  | 0.3        |          | 2                    | V       | coupled to GND or<br>externally biased within                                                                                                   |  |

| Single-Ended Input<br>Common-Mode<br>Voltage | $V_{CM}^{}$        | 0.25       | Ç        | V <sub>DD</sub> -1.2 | V       | V <sub>CM</sub> range                                                                                                                           |  |

| Differential Input Clock                     | Specifications     | s (CLKx/   | nCLKx )  |                      | 10      |                                                                                                                                                 |  |

| Differential Input<br>Voltage Swing          | $V_{\mathrm{ID}}$  | 0.15       | 7        | 1.3                  | SV      |                                                                                                                                                 |  |

| Differential Input                           |                    | 0.25       |          | $V_{DD}$ -0.9        | V       | V <sub>ID</sub> =800mV                                                                                                                          |  |

| Common-Mode                                  | $V_{CMD}^{(5)}$    | 0.25       | <u> </u> | V <sub>DD</sub> -1.1 | V       | V <sub>ID</sub> =350mV                                                                                                                          |  |

| Voltage                                      |                    | 0.25       | 60       | V <sub>DD</sub> -1.2 | V       | V <sub>ID</sub> =150mV                                                                                                                          |  |

| Differential Input High<br>Voltage           | $V_{\mathrm{IHD}}$ |            |          | $V_{DD}$             | V       |                                                                                                                                                 |  |

| Differential Input Low<br>Voltage            | $V_{\rm ILD}$      | 0          |          |                      | V       |                                                                                                                                                 |  |

|                                              |                    |            | -65      |                      | dBc     | F <sub>IN</sub> =1000MHz                                                                                                                        |  |

| Mux Isolation,                               | ISO <sub>IN</sub>  |            | -71      |                      | dBc     | F <sub>IN</sub> =500MHz                                                                                                                         |  |

| CLKin0 to CLKin                              | ISOIN              |            | -82      |                      | dBc     | F <sub>IN</sub> =200MHz                                                                                                                         |  |

| <b>\</b>                                     | _                  |            | -84      |                      | dBc     | F <sub>IN</sub> =100MHz                                                                                                                         |  |

| Input Frequency (CLK/                        | nCLK)              |            |          |                      |         |                                                                                                                                                 |  |

| Input Frequency<br>Range                     | $\mathrm{F_{IN}}$  | 0          |          | 2500                 | MHz     | Functional up to 2.5GHz,<br>Output frequency range<br>and timing specified per<br>output type (refer to<br>LVPECL, LVDS, HCSL,<br>LVCMOS output |  |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 8/21

| Parameters | Symbol | Value |  | Unit | Notes |                 |

|------------|--------|-------|--|------|-------|-----------------|

|            |        |       |  |      |       | specifications) |

- \* (2) CLKx/nCLKx represent CLK0/nCLK0 和 CLK1/nCLK1

- (3) For clock input frequency  $\geq$  100MHz, CLKx can be driven with single-ended (LVCMOS) input swing up to 3.3VPP. For clock input frequency < 100MHz, the single-ended input swing should be limited to  $2V_{PP}$  max to prevent input saturation (refer to Driving the Clock Inputs for interfacing 2.5V/3.3V LVCMOS clock input < 100MHz to CLKx).

- (4) CLKx driven single-ended (AC or DC coupled), nCLKx AC coupled to GND or externally biased within V<sub>CM</sub> range

- (5) AC coupled must be applied when  $V_{CM}$  of input signals exceed  $V_{CMD}$  Max..

$Table~6.~X_{IN}/X_{OUT}~Characteristics$   $Test~Condition:~-40^{\circ}C \leq TA \leq 85^{\circ}C, 3.15V \leq V_{DD} \leq 3.45V, 2.375V \leq V_{DDOX} \leq 2.625~or~3.135V \leq V_{DDOX} \leq 3.45V, 2.375V \leq 0.45V, 2.375V \leq 0.45V, 2.375V \leq 0.45V, 2.375V \leq 0.45V, 2.375V \leq$

| Parameters                        | Cb al                  | Value |             |      | T I \$4 | Notes                                   |

|-----------------------------------|------------------------|-------|-------------|------|---------|-----------------------------------------|

| rarameters                        | Symbol                 | Min.  | Тур.        | Max. | Unit    | Notes                                   |

| Crystal Input                     |                        |       |             |      |         |                                         |

| Crystal Mode                      |                        |       | Fundamental |      |         | \$                                      |

| Crystal Frequency<br>Input Range  | f <sub>XIN</sub> /XOUT | 10    | ~ ^         | 40   | MHz     |                                         |

| Effective Series                  | ESR                    |       |             | 200  | Ω       | 10MHz <f<sub>XIN≤30<br/>MHz</f<sub>     |

| Resistance                        | ESK                    | 125   |             | 36   | Ω       | 30MHz <f<sub>XIN&lt;40<br/>MHz</f<sub>  |

| Input Capacitance                 | $C_{XO}$               |       | 4           |      | pF      |                                         |

| Single-ended input                |                        |       |             | N    |         |                                         |

| External Clock Input<br>Frequency | $f_{ m XIN}$           | DC    | COP-        | 250  | MHz     | Single-Ended<br>Input, Xout<br>floating |

Table 7. LVDS Outputs Characteristics

Test Condition:  $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$ ,  $3.15\text{V} \le V_{DD} \le 3.45\text{V}$ ,  $2.375\text{V} \le V_{DDOX} \le 2.625$  or  $3.135\text{V} \le V_{DDOX} \le 3.45$ , CLK driven differentially, input slew rate  $\ge 3\text{V/ns}$

| Parameters                             | Crowhal                 | Value |      |      | T 7 24 | <b>N</b> T 4                                                                       |

|----------------------------------------|-------------------------|-------|------|------|--------|------------------------------------------------------------------------------------|

|                                        | Symbol                  | Min.  | Тур. | Max. | Unit   | Notes                                                                              |

| QAn/nQAn,QBn/nQBn                      |                         |       |      |      |        |                                                                                    |

| Maximum Output                         | E                       | 1000  | 1600 |      | MHz    | Full $V_{OD}$ Swing, $V_{OD} > 250 \text{mV}$ , $R_L = 100 \Omega$ differential    |

| Frequency                              | Fout-max                | 1500  | 2100 |      | MHz    | Reduced $V_{OD}$ Swing, $V_{OD} > 200 \text{mV}$ , $R_L = 100 \Omega$ differential |

| Output Voltage<br>Swing                | $V_{\mathrm{OD}}$       | 250   | 400  | 450  | mV     | $T_A = 25^{\circ}C$ , DC                                                           |

| Change in Magnitude of V <sub>OD</sub> | $\Delta { m V}_{ m OD}$ | -50   |      | 50   | mV     | Measurement, $R_L = 100\Omega$ differential                                        |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 9/21

| Parameters                                                     | Symbol                        | Value |        |       | Unit   | Notes                                                                                                                           |

|----------------------------------------------------------------|-------------------------------|-------|--------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| for Complementary Output States                                |                               |       |        |       |        |                                                                                                                                 |

| Output Offset<br>Voltage                                       | V <sub>OFFSET</sub>           | 1.125 | 1.25   | 1.375 | V      |                                                                                                                                 |

| Change in Magnitude of Voffset for Complementary Output States | $\Delta { m V}_{ m OFFSET}$   | -35   |        | 35    | mV     |                                                                                                                                 |

| Output Duty Cycle                                              | Duty<br>Cycle                 | 45    | 50     | 55    | %      | • . ()                                                                                                                          |

| Output Rise/Fall<br>Time, 20% to 80%                           | $t_{ m Rise}$ / $t_{ m Fall}$ |       | 175    | 300   | ps     | uniform transmission line up to 10 inches with $50\Omega$ characteristic impedance, $RL = 100\Omega$ differential, $C_L \le 5p$ |

| Propagation Delay                                              | $t_{\mathrm{Delay}}$          | 200   | 400    | 600   | ps     | RL = 100 $\Omega$ differential, C <sub>L</sub> $\leq$ 5pF                                                                       |

| Output Skew                                                    | $t_{ m Skew}$                 |       | 30     | 50    | ps     | Skew specified between any two CLKouts with the same buffer type. Load                                                          |

| Part-to-part Output<br>Skew                                    | $t_{\mathrm{PDP}}$            |       | 80     | 120   | ps     | conditions per output type are the same as propagation delay specifications.                                                    |

|                                                                |                               |       | 132    | ,     | fs     | F <sub>IN</sub> =100MHz<br>Slew Rate≥3V/ns<br>1MHz to 20MHz                                                                     |

|                                                                |                               | A     | 103    |       | fs     | F <sub>IN</sub> =156.25MHz<br>Slew Rate≥3V/ns<br>1MHz to 20MHz                                                                  |

| Additive RMS Jitter                                            | tı                            |       | 33     |       | fs     | F <sub>IN</sub> =625MHz<br>Slew Rate≥3V/ns<br>1MHz to 20MHz                                                                     |

| _                                                              |                               | )     | 138    | 2/-   | fs     | F <sub>IN</sub> =100MHz<br>Slew Rate≥3V/ns<br>10kHHz to 20MHz                                                                   |

|                                                                | )                             |       | 99     |       | fs     | F <sub>IN</sub> =156.25MHz<br>Slew Rate≥3V/ns<br>10kHHz to 20MHz                                                                |

|                                                                |                               |       | -159.5 |       | dBc/Hz | F <sub>IN</sub> =100MHz<br>Slew Rate≥3V/ns                                                                                      |

| Noise Floor<br>f <sub>OFFSET</sub> ≥10MHz                      | NF                            |       | -157   |       | dBc/Hz | F <sub>IN</sub> =156.25MHz<br>Slew Rate≥3V/ns                                                                                   |

|                                                                |                               |       | -152.5 |       | dBc/Hz | F <sub>IN</sub> =625MHz<br>Slew Rate≥3V/ns                                                                                      |

# Table 8. LVPECL Outputs Characteristics

Test Condition:  $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$ ,  $3.15\text{V} \le V_{DD} \le 3.45\text{V}$ ,  $2.375\text{V} \le V_{DDOX} \le 2.625$  or  $3.135\text{V} \le V_{DDOX} \le 3.45$ , CLK driven differentially, input slew rate  $\ge 3\text{V/ns}$ .

|                 | J , 1  |       |      |      |      |       |

|-----------------|--------|-------|------|------|------|-------|

| Donomotors      | Symbol | Value |      |      | Unit | Notes |

| Parameters Symb | Symbol | Min.  | Тур. | Max. | UIII | Notes |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 10 / 21

| Parameters                      | Symbol               | Value                      |                            |                      | Unit | Notes                                                                                                                                                                                                                                                   |

|---------------------------------|----------------------|----------------------------|----------------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QAn/nQAn,QBn/nQ                 | QBn                  |                            |                            |                      |      |                                                                                                                                                                                                                                                         |

|                                 |                      | 1000                       | 1200                       |                      | MHz  | Full $V_{OD}$ Swing , $V_{OD} \geqslant$ 600mV, $R_L = 100\Omega$ differential, $V_{DDOX} = 3.3$ V, $R_T = 160\Omega$ to GND                                                                                                                            |

| Maximum Output                  | F <sub>OUT</sub> -   | 750                        | 1000                       |                      | MHz  | Full $V_{OD}$ Swing , $V_{OD} \geqslant$ 600mV, $R_L = 100\Omega$ differential, $V_{DDOX} = 2.5$ V, $R_T = 91\Omega$ to GND                                                                                                                             |

| Frequency                       | MAX                  | 1500                       | 2200                       |                      | MHz  | $\label{eq:Reduced Vod Swing} \begin{split} & Reduced \ V_{OD} \ Swing \ , \ V_{OD} \\ & \geqslant 400 mV, \ R_L = 100\Omega \\ & \text{differential}, \ V_{DDOX} \!\!=\!\! 3.3V, \\ & R_T \!\!=\! 160\Omega \ \text{to GND} \end{split}$               |

|                                 |                      | 1500                       | 2200                       |                      | MHz  | $\begin{split} & \text{Reduced } V_{\text{OD}}  \text{Swing , } V_{\text{OD}} \\ & \geqslant 400 \text{mV, } R_L = 100 \Omega \\ & \text{differential, } V_{\text{DDOX}} \!\!=\!\! 2.5 \text{V,} \\ & R_T \!\!=\! 91 \Omega \text{ to GND} \end{split}$ |

| Output Voltage<br>Swing         | $V_{\mathrm{OD}}$    | 600                        | 830                        | 1000                 | mV   | 7 ) 250G P.G                                                                                                                                                                                                                                            |

| Output High<br>Voltage          | $V_{\mathrm{OH}}$    | V <sub>DDOX</sub> -<br>1.2 | V <sub>DDOX</sub> -<br>0.9 | $V_{\rm DDOX}$ - 0.7 | V    | $T_A = 25^{\circ}\text{C}$ , DC<br>Measurement, $R_T = 50\Omega$ to $V_{DDO}$ - $2V$                                                                                                                                                                    |

| Output Low<br>Voltage           | $V_{OL}$             | $V_{\rm DDOX}$ - 2.0       | V <sub>DDOX</sub> -        | $V_{\rm DDOX}$ - 1.5 | V    | V DDO - 2 V                                                                                                                                                                                                                                             |

| Output Duty<br>Cycle            | Duty<br>Cycle        | 45                         | 50                         | 55                   | %    | S.                                                                                                                                                                                                                                                      |

| Output Rise Time, 20% to 80%    | $t_{ m Rise}$        |                            | 250                        | 350                  | ps   | $R_T = 160\Omega$ to GND, uniform transmission line up to 10                                                                                                                                                                                            |

| Output Fall Time,<br>80% to 20% | t <sub>Fall</sub>    |                            | 180                        | 300                  | ps   | inches with $50\Omega$ characteristic impedance, $R_L$ = $100\Omega$ differential, $C_L \le 5pF$                                                                                                                                                        |

| Propagation Delay               | $t_{\mathrm{Delay}}$ | 180                        | 360                        | 540                  | ps   | $R_T = 160 \Omega$ to GND, $R_L = 50\Omega$ differential, $C_L \le 5pF$                                                                                                                                                                                 |

| Output Skew                     | $t_{ m Skew}$        |                            | 30                         | 50                   | ps   | Skew specified between any two CLKouts with the same buffer type. Load conditions                                                                                                                                                                       |

| Part-to-part<br>Output Skew     | t <sub>PDP</sub>     |                            | 80                         | 120                  | ps   | per output type are the same<br>as propagation delay<br>specifications.                                                                                                                                                                                 |

|                                 |                      |                            | 55                         |                      | fs   | F <sub>IN</sub> =100MHz<br>Slew Rate≥3V/ns 1MHz to<br>20MHz                                                                                                                                                                                             |

|                                 |                      |                            | 35                         |                      | fs   | F <sub>IN</sub> =156.25MHz<br>Slew Rate≥3V/ns 1MHz to<br>20MHz                                                                                                                                                                                          |

| Additive RMS<br>Jitter          | t <sub>J</sub>       |                            | 25                         |                      | fs   | F <sub>IN</sub> =625MHz<br>Slew Rate≥3V/ns 1MHz to<br>20MHz                                                                                                                                                                                             |

|                                 |                      |                            | 60                         | 98                   | fs   | F <sub>IN</sub> =100MHz<br>Slew Rate≥3V/ns 10kHHz to<br>20MHz                                                                                                                                                                                           |

|                                 |                      |                            | 30                         | 78                   | fs   | F <sub>IN</sub> =156.25MHz<br>Slew Rate≥3V/ns 10kHHz to                                                                                                                                                                                                 |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 11/21

| Parameters                                | Symbol | Value | Unit | Notes                   |

|-------------------------------------------|--------|-------|------|-------------------------|

|                                           |        |       |      | 20MHz                   |

| Noise Floor<br>f <sub>OFFSET</sub> ≥10MHz |        | -161  | dBc/ | F <sub>IN</sub> =100MHz |

|                                           |        | 101   | Hz   | Slew Rate≥3V/ns         |

|                                           | NF     | -159  | dBc/ | $F_{IN}=156.25MHz$      |

|                                           |        | -139  | Hz   | Slew Rate≥3V/ns         |

|                                           |        | 154   | dBc/ | F <sub>IN</sub> =625MHz |

|                                           |        | -154  | Hz   | Slew Rate≥3V/ns         |

Table 9. HCSL Outputs Characteristics

Test Condition:  $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$ ,  $3.15\text{V} \le V_{DD} \le 3.45\text{V}$ ,  $2.375\text{V} \le V_{DDOX} \le 2.625$  or  $3.135\text{V} \le V_{DDOX} \le 3.45$ , CLK driven differentially, input slew rate  $\ge 3\text{V/ns}$ .

| D .                                       | G 1 1                       | Value |      |      | <b>T</b> T •4 | NT 4                                                                                                    |

|-------------------------------------------|-----------------------------|-------|------|------|---------------|---------------------------------------------------------------------------------------------------------|

| Parameters                                | Symbol                      | Min.  | Тур. | Max. | Unit          | Notes                                                                                                   |

| QAn/nQAn,QBn/nQF                          | 3n                          |       |      |      |               |                                                                                                         |

| Output Frequency<br>Range                 | F <sub>OUT</sub>            | 0     |      | 400  | MHz           |                                                                                                         |

| Absolute Crossing<br>Voltage              | V <sub>CROSS</sub>          | 160   | 350  | 460  | mV            | $R_L = 50\Omega$ to GND, $C_L \le 5pF$                                                                  |

| Total Variation of $V_{CROSS}$            | $\Delta V_{CROSS}$          |       |      | 140  | mV            | ) <u></u>                                                                                               |

| Output High<br>Voltage                    | $V_{\mathrm{OH}}$           | 520   | 750  | 920  | mV            | $T_A = 25$ °C, DC Measurement, $R_T$                                                                    |

| Output Low<br>Voltage                     | $V_{OL}$                    | -150  | 0.5  | 150  | mV            | $=50\Omega$ to GND                                                                                      |

| Output Duty Cycle                         | Duty<br>Cycle               | 45    | 50   | 55   | %             | 9011                                                                                                    |

| Output Rise/Fall<br>Time, 20% to 80%      | $t_{ m Rise} / t_{ m Fall}$ |       | 300  | 500  | ps            |                                                                                                         |

| Propagation Delay                         | $t_{ m Delay}$              | 295   | 590  | 885  | ps            | $R_T = 50\Omega$ to GND, $C_L \le 5pF$                                                                  |

| Output Skew                               | $t_{ m Skew}$               |       | 30   | 50   | ps            | Skew specified between any two CLKouts with the same buffer                                             |

| Part-to-part Output<br>Skew               | t <sub>PDP</sub>            |       | 80   | 120  | ps            | type. Load conditions per output type are the same as propagation delay specifications.                 |

|                                           | ty nov                      |       | 0.03 | 0.15 | ps            | PCIe Gen 3, PLL BW = 2-5MHz,<br>CDR = 10MHz, $F_{IN}$ =100MHz<br>Slew Rate $\geq$ 0.6V/ns               |

|                                           | t <sub>J_PCIe</sub>         |       | 0.03 | 0.05 | ps            | PCIe Gen 4, PLL BW = 2-5MHz,<br>CDR = 10MHz, $F_{IN}$ =100MHz<br>Slew Rate $\geq$ 1.8V/ns               |

| Additive RMS Jitter                       |                             |       | 77   |      | fs            | $V_{DDO}=3.3V,R_T=50\Omega$ to GND<br>$F_{IN}=100MHz$<br>Slew Rate $\geqslant 3V/ns$<br>1MHz to $20MHz$ |

|                                           | t <sub>J</sub>              |       | 86   |      | fs            | $V_{DDO} = 3.3V$ , $R_T = 50\Omega$ to GND $F_{IN} = 156.25$ Hz Slew Rate $\geq 3V/ns$ 1MHz to 20MHz    |

| Noise Floor<br>f <sub>OFFSET</sub> ≥10MHz | NF                          |       | -161 |      | dBc/<br>Hz    | $V_{DDO} = 3.3V, R_T = 50\Omega$ to GND $F_{IN}=100MHz$                                                 |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 12/21

| Parameters | Symbol | Value | Unit       | Notes                                                                                                               |

|------------|--------|-------|------------|---------------------------------------------------------------------------------------------------------------------|

|            |        |       |            | Slew Rate ≥ 3V/ns                                                                                                   |

|            |        | -156  | dBc/<br>Hz | $V_{DDO} = 3.3 \text{V}, R_T = 50 \Omega \text{ to GND}$ $F_{IN} = 156.25 \text{Hz}$ Slew Rate $\geq 3 \text{V/ns}$ |

# Table 10. LVCMOS Outputs Characteristics

Test Condition:  $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$ ,  $3.15\text{V} \le V_{DD} \le 3.45\text{V}$ ,  $2.375\text{V} \le V_{DDOX} \le 2.625$  or  $3.135\text{V} \le V_{DDOX} \le 3.45$ , CLK driven differentially, input slew rate  $\ge 3\text{V/ns}$ .

| Donomotors                                    | Cymbal                   |                            | Value |      | Unit       | Notes                                                                                |  |

|-----------------------------------------------|--------------------------|----------------------------|-------|------|------------|--------------------------------------------------------------------------------------|--|

| Parameters                                    | Symbol                   | Min.                       | Тур.  | Max. | Omt        |                                                                                      |  |

| Output High Voltage                           | $V_{\mathrm{OH}}$        | V <sub>DDOX</sub> -<br>0.1 |       |      | V          | 1mA Load                                                                             |  |

| Output Low Voltage                            | $V_{\mathrm{OL}}$        |                            |       | 0.1  | V          |                                                                                      |  |

| Output High Cumont                            | T                        |                            | 28    |      | mA         | $V_{DDOX}=3.3V$                                                                      |  |

| Output High Current                           | $I_{OH}$                 |                            | 20    |      | mA         | V <sub>DDOX</sub> =2.5V                                                              |  |

| Output I ou Cumont                            | т                        |                            | 28    |      | mA         | V <sub>DDOX</sub> =3.3V                                                              |  |

| Output Low Current                            | $I_{OL}$                 |                            | 20    |      | mA         | V <sub>DDOX</sub> =2.5V                                                              |  |

| Output Frequency<br>Range(                    | F <sub>OUT</sub>         | 0                          | 0     | 300  | MHz        | CL ≤ 5pF                                                                             |  |

| Output Duty Cycle                             | Duty<br>Cycle            | 45                         | 50    | 55   | %          | 50% input clock duty cycle                                                           |  |

| Output Rise Time,<br>20% to 80%               | $t_{ m Rise}$            | 5                          | 225   | 500  | ps         | 250MHz, uniform transmission line up to 10 inches with 50Ω characteristic impedance, |  |

| Output Fall Time, 20% to 80%                  | t <sub>Fall</sub>        |                            | 225   | 400  | ps         | $R_L = 50\Omega$ to GND, $C_L \le 5pF$                                               |  |

| Propagation Dalay                             |                          | 900                        | 1475  | 2300 | ps         | $V_{DDOX}$ =3.3V, $CL \leq 5pF$                                                      |  |

| Propagation Delay                             | t <sub>Delay</sub>       | 1000                       | 1550  | 2700 | ps         | $V_{DDOX}$ =2.5V, CL $\leq$ 5pF                                                      |  |

| Additive RMS Jitter,<br>BW = 1MHz to<br>20MHz | t <sub>J</sub>           |                            | 132   |      | fs         | $V_{DDO} = 3.3V$ $C_L \le 5pF F_{IN}=100MHz$                                         |  |

| Noise Floor,<br>$f_{OFFSET} \ge 10MHz$        |                          |                            | -158  |      | dBc/<br>Hz | Slew Rate ≥ 3V/ns                                                                    |  |

| Output<br>Enable/Disable Time                 | $t_{\rm EN}/t_{\rm DIS}$ |                            |       | 3    | Cycle      | $C_L \leqslant 5pF$                                                                  |  |

https://www.dptel.com/

TEL:0086-0769-88010888

Songshan Lake, Dongguan, Guangdong

# 5 FUNCTION DESCRIPTION

## 5.1 Control Signals

INS6310A has three groups of control signals:

- ➤ Input Selection

- Output Type Selection

- Reference Output Enable

Clock input selection is controlled using the SEL0 and SEL1 pins as shown in Table 11. Refer to Driving the Clock Inputs for clock input requirements. When CLK0 or CLK1 is selected, the crystal circuit is powered down. When Xin is selected, the crystal oscillator will start-up and its clock will be distributed to all outputs. Refer to Crystal Interface for more information. Alternatively, Xin may be driven by a single-ended clock, up to 250MHz, instead of a crystal.

Table 11. Input Selection

| SEL[1] | SEL[0] | Selected Input   |

|--------|--------|------------------|

| 0      | 0      | CLK0/nCLK0       |

| 0      | 1      | CLK1/nCLK1       |

| 1      | X      | $X_{IN}/X_{OUT}$ |

The differential output buffer type for Bank A and Bank B outputs can be separately configured using the OTYPEA[1:0] and OTYPEB[1:0] inputs, respectively, as shown in table 12. For applications where all differential outputs are not needed, any unused output pin should be left floating with a minimum copper length to minimize capacitance and potential coupling and reduce power consumption. If an entire output bank will not be used, it is recommended to disable (Hi-Z) the bank to reduce power. Refer to Termination and Use of Clock Drivers for more information on output interface and termination techniques.

Table 12. Output Type Selection

| OTYPEx[1] | OTYPEx[0] | Output Type<br>(BankA or B) |

|-----------|-----------|-----------------------------|

| 0         | 0         | LVPECL                      |

| 0         | 1         | LVDS                        |

| 1         | 0         | HCSL                        |

| 1         | 1         | Hi-Z                        |

Notes: OTYPEx represent OTYPEA and OTYPEB

The reference output (REFOUT) provides a LVCMOS copy of the selected input clock. The LVCMOS output high level is referenced to the  $V_{DDO}$  voltage. REFOUT can be enabled or disabled using the enable input pin, REFOUT\_OE, as shown in Table 13.

Table 13. Reference Output Enable

|           | •                      |

|-----------|------------------------|

| REFOUT_OE | Reference Output State |

| 0         | Hi-Z                   |

| 1         | Enabled                |

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 14/21

#### 5.2 Input Clocks

CLK/nCLK differential inputs: The INS6310A has two differential inputs (CLK0/nCLK0 and CLK1/nCLK1) that can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, CML, SSTL and other differential and single-ended signals that meet the input requirements specified in ELECTRICAL CHARACTERISTICS. The device can accept a wide range of signals due to its wide input common mode voltage range ( $V_{CM}$ ) and input voltage swing ( $V_{ID}$ ). It is recommended that the inputs have a high slew rate of 3 V/ns (differential) or higher in case to degrade the noise floor and jitter. For this reason, a differential input signal is recommended over single-ended because it typically provides higher slew rate and common-mode noise rejection.

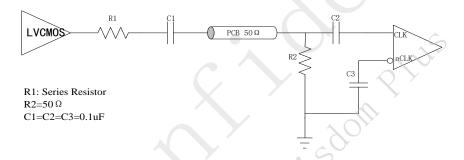

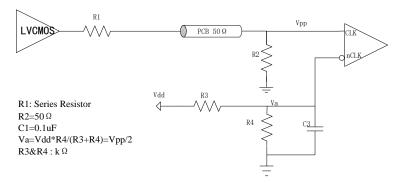

**CLK/nCLK** single-ended inputs: It is possible to drive it with a single-ended clock. For large single-ended input signals, such as 3.3V or 2.5V LVCMOS, a  $50\Omega$  load resistor should be placed near the input for signal attenuation to prevent input overdrive as well as for line termination to minimize reflections. The CLK input has an internal bias voltage of about 1.4V, so the input can be AC coupled as shown in Figure3. The output impedance of the LVCMOS driver plus R1 should be close to  $50~\Omega$  to match the characteristic impedance of the transmission line and load termination.

Figure 3. Single-Ended LVCMOS input, AC Coupling

A single-ended clock may also be DC coupled to CLKx as shown in Figure 4. A  $50\Omega$  load resistor should be placed near the CLKx input for signal attenuation and line termination. Because half of the single-ended swing of the driver  $(V_{O,PP}/2)$  drives CLKx, nCLKx should be externally biased to the midpoint voltage of the attenuated input swing  $((V_{O,PP}/2)\times0.5)$ . The external bias voltage should be within the specified input common voltage  $(V_{CM})$  range. This can be achieved using external biasing resistors in the  $k\Omega$  range (R3 and R4) or another low-noise voltage reference. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.

Figure 4. Single-Ended LVCMOS input, DC Coupling

TEL:0086-0769-88010888 https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 15/21

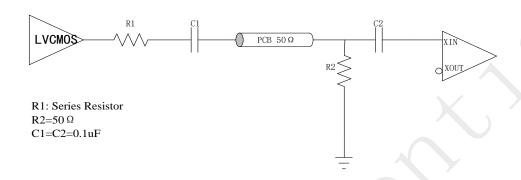

X<sub>IN</sub>/X<sub>OUT</sub>: If the crystal oscillator circuit is not used, it is possible to drive the Xin input with a single-ended external clock as shown in Figure 5. The input clock should be AC coupled to the Xin pin, which has an internally generated input bias voltage, and the Xout pin should be left floating. While Xin provides an alternative input to multiplex an external clock, it is recommended to use either differential input (CLKx) since it offers higher operating frequency, better common mode, improved power supply noise rejection and greater performance over supply voltage and temperature variations.

Figure 5. X<sub>IN</sub> Single-Ended LVCMOS Clock

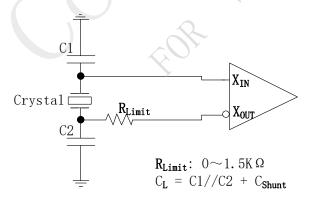

The INS6310A has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal interface is shown in Figure 6, while CL is specified for the crystal and  $C_{Shunt}$  is the sum of  $C_{IN}$  and PCB  $C_{STRAY}$ .

As shown in Figure 6, an external resistor,  $R_{LIMIT}$ , can be used to limit the crystal drive level if necessary. If the power dissipated in the selected crystal is higher than the drive level specified for the crystal with  $R_{LIMIT}$  shorted, then a larger resistor value is mandatory to avoid overdriving the crystal. However, if the power dissipated in the crystal is less than the drive level with  $R_{LIMIT}$  shorted, then a zero value for  $R_{LIMIT}$  can be used. As a starting point, a suggested value for RLIM is  $1.5k\Omega$ .

Figure 6. X<sub>IN</sub>/X<sub>OUT</sub> Crystal Interface

# 5.3 CLOCK OUTPUTS

INS6310A has two banks of 5 differential outputs and one LVCMOS output which can be independently supplied with 3.3V or 2.5V.

TEL:0086-0769-88010888 https://www.dptel.com/ Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 16 / 21

Table 14. Clock Outputs

| Bank   | Outputs                 |

|--------|-------------------------|

| Bank A | QA0, QA1, QA2, QA3, QA4 |

| Bank B | QB0, QB1, QB2, QB3, QB4 |

| REFOUT | REFOUT                  |

Table 2 following will be the state of the outputs.

Table 15. Input Vs. Output States

| SEL[1]     | Input Clock                     | Output State |

|------------|---------------------------------|--------------|

| Logic Low  | CLKx=Open nCLKx=Open            | Logic Low    |

|            | CLK= Logic High nCLK= Logic Low | Logic High   |

|            | CLK= Logic Low nCLK= Logic High | Logic Low    |

|            | CLK and nCLK short              | Logic Low    |

| Logic High | X <sub>IN</sub> = Logic High    | Logic Low    |

|            | X <sub>IN</sub> = Logic Low     | Logic High   |

**Notes**

Unused outputs should be left floating with a minimum copper length to minimize capacitance. In this way, this output will consume minimal output current because it has no load.

#### 5. 3. 1 Termination and Use of Clock Drivers

When terminating clock drivers keep in mind these guidelines for optimum phase noise and jitter performance:

- Transmission line theory should be followed for good impedance matching to prevent reflections.

- Clock drivers should be presented with the proper loads.

- LVDS outputs are current drivers and require a closed current loop.

- ightharpoonup HCSL drivers are switched current outputs and require a DC path to ground via  $50\Omega$  termination.

- LVPECL outputs are open emitter and require a DC path to ground.

- Receivers should be presented with a signal biased to their specified DC bias level (common mode voltage) for proper operation. Some receivers have self-biasing inputs that automatically bias to the proper voltage level; in this case, the signal should normally be AC coupled.

It is possible to drive a non-LVPECL or non-LVDS receiver with a LVDS or LVPECL driver as long as the above guidelines are followed. Check the datasheet of the receiver or input being driven to determine the best termination and coupling method to be sure the receiver is biased at the optimum DC voltage (common mode voltage)

### **Termination for LVDS Driver**

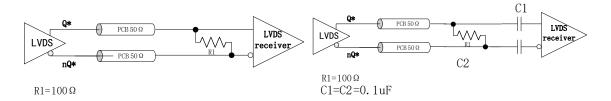

For DC coupled operation, terminate with  $100\Omega$  as close as possible to the LVDS receiver. For AC coupled operation by adding DC blocking capacitors, the load termination resistor and AC coupling capacitors should be placed as close as possible to the receiver inputs to minimize stub length, as shown in Figure 7

TEL:0086-0769-88010888

https://www.dptel.com/

Songshan Lake, Dongguan, Guangdong

Figure 7. LVDS DC&AC Coupling

#### **Termination for LVPECL Driver**

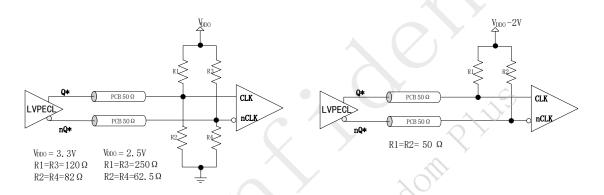

For DC coupled operation of an LVPECL driver, terminate with 50 $\Omega$  to  $V_{DDO}$  - 2V. Alternatively terminate with a Thevenin equivalent circuit for  $V_{DDO}$  (output driver supply voltage) = 3.3V and 2.5V. In the Thevenin equivalent circuit, the resistor dividers set the output termination voltage ( $V_{TT}$ ) to  $V_{DDO}$  - 2V. as shown in Figure 8

Figure 8. LVPECL DC Coupling

When AC coupling an LVPECL signal use  $160\Omega$  emitter resistors (or  $91\Omega$  for  $V_{DDO}=2.5V$ ) close to the LVPECL driver to provide a DC path to ground as shown in Figure 9. For proper receiver operation, the signal should be biased to the DC bias level (common mode voltage) specified by the receiver. The typical DC bias voltage (common mode voltage) for LVPECL receivers is 2.0V. Alternatively, a Thevenin equivalent circuit forms a valid termination as shown in Figure 9 for  $V_{DDO}=3.3V$  and 2.5V. This Thevenin circuit is different from the DC coupled example in Figure 8, since the voltage divider is setting the receiver input common mode voltage.

Figure 9. LVPECL AC coupling, Thevenin equivalent

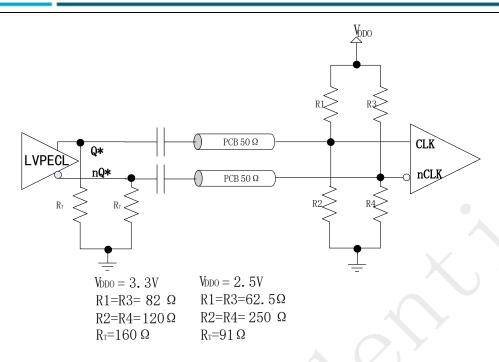

#### **Termination for HSCL Driver**

For DC coupled operation of an HCSL driver, terminate with  $50\Omega$  to ground near the driver output as shown in Figure 10. Series resistors,  $R_S$ , may be used to limit overshoot due to the fast transient current. Because HCSL drivers require a DC path to ground, AC coupling is not allowed between the output drivers and the  $50\Omega$  termination resistors.

Figure 10. HCSL Operation, DC Coupling

TEL:0086-0769-88010888 https://www.dptel.com/ Songshan Lake, Dongguan, Guangdong

Version: 1.2 DAPU Confidential Page: 19 / 21

# 5.4 Power Supply

The INS6310A operates from a 3.3V core supply and 3 independent 3.3V/2.5V output supplies.

VDD is INS6310A core supply voltage support 3.3V.

VDDOA, VDDOB and VDDOC are power supply for Bank A, B, C output buffers respectively. They can operate from 3.3V or 2.5V.

#### **Notes**

- $V_{DDO}$  should be less than or equal to  $V_{DD}$  ( $V_{DDO} \leq V_{DD}$ )

- .1uF or 0.01uF bypass capacitors should be placed very close to each supply pin

- 1uF to 10uF Decoupling capacitors should be placed nearby

Version: 1.2 DAPU Confidential Page: 20/21

https://www.dptel.com/

TEL:0086-0769-88010888

Songshan Lake, Dongguan, Guangdong

# 6 ENVIRONMENT

Table 16. ENVIRONMENT CONDITIONS

| Parameters | Value  | Unit | Notes                                         |  |

|------------|--------|------|-----------------------------------------------|--|

| ESD Level  | ±2000V | V    | HBM, Refer to ANSI/ESDA/JEDEC JS-001-2010     |  |

|            | ±800V  | V    | CDM, Refer to JEDEC specification JESD22-C101 |  |

\* HBM: Human body model

CDM: Charged-device model

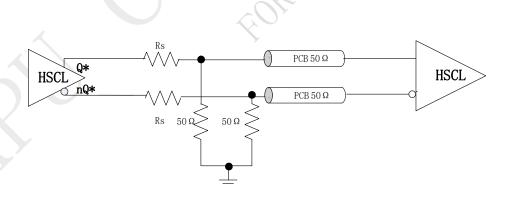

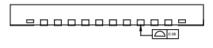

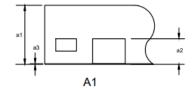

# 7 PACKAGE OUTLINE

TOP VIEW

Version: <u>1.2</u>

| COMMON DIMENSIONS             |         |      |      |  |  |  |  |

|-------------------------------|---------|------|------|--|--|--|--|

| (UNITS OF MEASURE=MILLIMETER) |         |      |      |  |  |  |  |

| SYMBOL                        | MIN     | NOM  | MAX  |  |  |  |  |

| Α                             | 6.90    | 7.00 | 7.10 |  |  |  |  |

| В                             | 6.90    | 7.00 | 7.10 |  |  |  |  |

| D                             | 5.20    | 5.30 | 5.40 |  |  |  |  |

| С                             | 5.20    | 5.30 | 5.40 |  |  |  |  |

| E                             | 0.35    | 0.45 | 0.55 |  |  |  |  |

| F                             | 0.30    | 0.40 | 0.50 |  |  |  |  |

| R                             | 0.09    | _    | _    |  |  |  |  |

| а                             | 0.40    | 0.50 | 0.60 |  |  |  |  |

| b                             | 0.20    | 0.25 | 0.30 |  |  |  |  |

| a1                            | 0.70    | 0.75 | 0.80 |  |  |  |  |

| a2                            | 0.20REF |      |      |  |  |  |  |

| a3                            | 0.00    | 0.02 | 0.05 |  |  |  |  |

SIDE VIEW A1

Figure 11. Package Outline Diagram

TEL:0086-0769-88010888 https://www.dptel.com/ Songshan Lake, Dongguan, Guangdong