# I2C Programmable Any-Frequency CMOS Clock Generator

### **FEATURES**

- Generates up to 3 non-integer-related frequencies from 2.5KHz to 250MHz

- I2C user definable configuration

- Exact frequency synthesis at each output (0 ppm error)

- Low output period jitter: <70pS (typ.)

- Configurable spread spectrum selectable at each output

- Operates from a low-cost, fixed frequency crystal: 25 or 27MHz

- Single-ended clock input accepts 2.8 to 40MHz

- Supports static phase offset

- Programmable rise/fall time control

- Glitch-less frequency changes

- Separate voltage supply pins provide level translation:

- Core VDD: 2.5 or 3.3V

- Output VDDO: 1.8, 2.5 or 3.3V

- Excellent PSRR eliminates external power supply filtering

- Very low power consumption

- Adjustable output delay

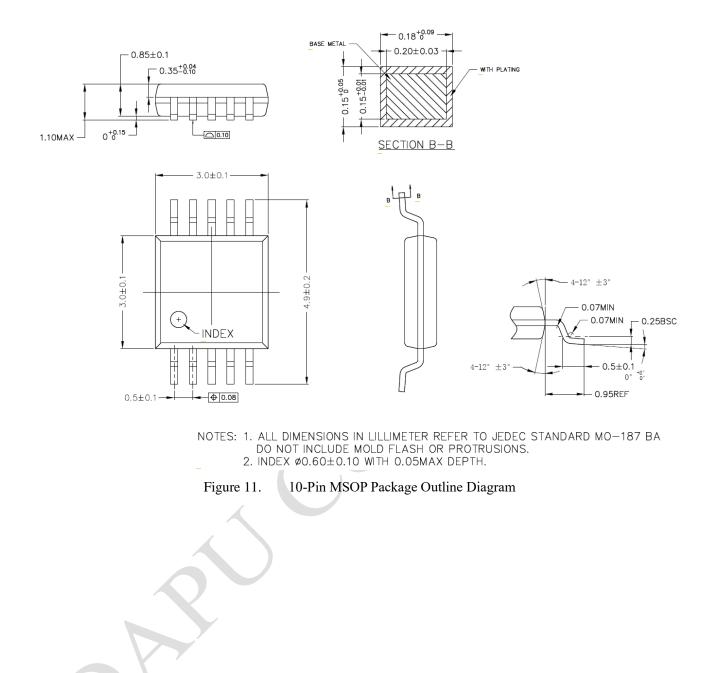

- Package type: MSOP10

- PCIE Gen 1 compatible

- Supports HCSL compatible swing) **APPLICATIONS**

- HDTV, DVD/Blue-ray, Set-top box

- Audio/video equipment, gaming

- Printers, scanners, projectors

- Handheld Instrumentation

- Residential gateways

- Networking/Communication

- Servers, Storage

- XO Replacement

### **GENERAL DESCRIPTIONS**

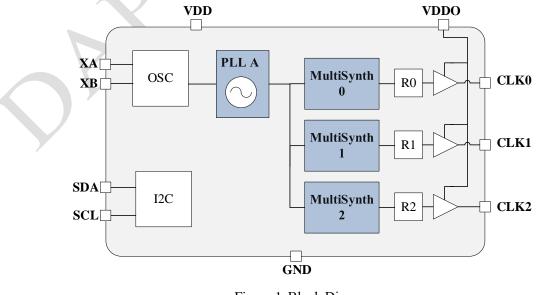

The INS8D5351A-GT is an I2C configurable clock generator that is ideally suited for replacing crystals, crystal oscillators, phase-locked loops (PLLs), and fanout buffers in cost-sensitive applications.

Based on a PLL+ high resolution MultiSynth fractional divider architecture, the INS8D5351A-GT can generate any frequency up to 250MHz on each of its outputs with 0ppm error. The INS8D5351A-GT can generate up to 3 free-running clocks using an internal oscillator for replacing crystals and crystal oscillators.

Figure 1. Block Diagram

## Contents

| 1.  | PINC | OUTS                                | 3  |

|-----|------|-------------------------------------|----|

| 2.  | ELEC | CTRICAL PARAMETER                   | 3  |

| 2   | .1   | Absolute Maximum Ratings            | 3  |

| 2   | .2   | Recommended Operating Conditions    | 4  |

| 2   | .3   | DC CHARACTERISTICS                  |    |

| 2   | .4   | AC CHARACTERISTICS                  | 5  |

| 2   | .5   | I <sup>2</sup> C SPECIFICATION      | 6  |

| 3.  | FUN  | ICTIONAL DESCRIPTION                | 7  |

| 3   | .1   | INPUT STAGE                         |    |

| 3   | .2   | Synthesis Stages                    | 8  |

| 3   | .3   | Output Stage                        | 8  |

| 4.  | CON  | IFIGURING THE INS8D5351A-GT         |    |

| 4   | .1   | I2C BUS INTERFACE                   | 9  |

| 4   | .2   | WRITE A CUSTOM CONFIGURATION TO RAM | 12 |

| 5.  | түрі | ICAL APPLICATION                    | 13 |

| 6.  |      | IGN CONSIDERATIONS                  |    |

| 0.  |      |                                     |    |

| 7.  | MEC  | CHANICAL STRUCTURE (MM)             | 15 |

| APP |      | X-1                                 | 17 |

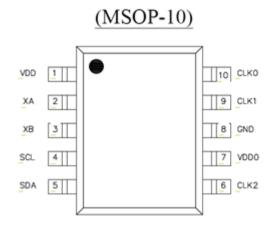

## 1. Pinouts

Figure 2. Pinout Diagram (Top view)

|        | Table1. Pin Descriptions |      |                                                      |  |  |  |  |  |  |  |

|--------|--------------------------|------|------------------------------------------------------|--|--|--|--|--|--|--|

| Number | Name                     | Туре | Description                                          |  |  |  |  |  |  |  |

| 1      | VDD                      | Р    | Core voltage power supply pin.                       |  |  |  |  |  |  |  |

| 2      | XA                       | Ι    | Input pin for external crystal.                      |  |  |  |  |  |  |  |

| 3      | XB                       | 0    | Output pin for external crystal.                     |  |  |  |  |  |  |  |

|        |                          |      | Serial clock input for the I2C bus. This pin must be |  |  |  |  |  |  |  |

| 4      | SCL                      | I    | pulled up to VDD using a pull-up resistor of at      |  |  |  |  |  |  |  |

|        |                          |      | least 1KΩ.                                           |  |  |  |  |  |  |  |

|        |                          |      | Serial data input for the I2C bus. This pin must be  |  |  |  |  |  |  |  |

| 5      | SDA                      | I/O  | pulled up to VDD using a pull-up resistor of at      |  |  |  |  |  |  |  |

|        |                          |      | least 1KΩ                                            |  |  |  |  |  |  |  |

| б      | CLK2                     | 0    | Output clock 2                                       |  |  |  |  |  |  |  |

| 7      | VDDO                     | P    | Output voltage power supply pin for CLK0, CLK1       |  |  |  |  |  |  |  |

| /      | VDDO                     | Р    | and CLK2.                                            |  |  |  |  |  |  |  |

| 8      | GND                      | Р    | Ground                                               |  |  |  |  |  |  |  |

| 9      | CLK1                     | 0    | Output clock 1.                                      |  |  |  |  |  |  |  |

| 10     | CLK0                     | 0    | Output clock 0.                                      |  |  |  |  |  |  |  |

Notes: I = Input, O = Output, P = Power.

## 2. Electrical Parameter

### 2.1 Absolute Maximum Ratings

### Table2. Absolute Maximum Ratings

Stresses beyond below listed absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

TEL:0086-0769-88010888 https://www.dptel.com/

| Parameter                                        | Symbol                | Rating        | Unit | Comments   |

|--------------------------------------------------|-----------------------|---------------|------|------------|

| DC Supply Voltage                                | $V_{DD\_MAX}$         | -0.3~3.8      | v    | VDD, VDDO  |

| Output Voltage                                   | Vout_clk              | -0.3~VDDO+0.3 | v    | (CLK0/1/2) |

| Input Voltage                                    | V <sub>IN_CLKIN</sub> | -0.3~3.8      | V    | SCL, SDA   |

| Input Voltage                                    | V <sub>IN_XA/XB</sub> | -0.3~1.3      | v    | XA, XB     |

| Junction Temperature                             | $T_J$                 | -55~150       | °C   |            |

| Soldering Temperature                            | $T_{PK}$              | 260           | °C   |            |

| Soldering Temperature Time at $T_{PK}$           | $T_P$                 | 20~40         | S    |            |

| Thermal Resistance Junction to Ambient of MSOP10 | JA                    | 131           | °C/W | Still air  |

| ESD                                              |                       | ±2000         | V    |            |

### 2.2 Recommended Operating Conditions

### Table3. Recommended Operating Conditions

All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise noted. VDD and VDDO can be operated at independent voltages. Power supply sequencing for VDD and VDDO requires that VDDO be powered up either before or at the same time as VDD.

| Parameter             | Symbol           |      | Unit |      |     |

|-----------------------|------------------|------|------|------|-----|

| rarameter             | Symbol           | Min. | Тур. | Max. | Umt |

| Core Surrely Voltors  | V                | 3.0  | 3.3  | 3.6  | V   |

| Core Supply Voltage   | V <sub>DD</sub>  | 2.25 | 2.5  | 2.75 | V   |

|                       | V <sub>DDO</sub> | 1.71 | 1.8  | 1.89 | V   |

| Output Buffer Voltage |                  | 2.25 | 2.5  | 2.75 | V   |

|                       |                  | 3.0  | 3.3  | 3.6  | V   |

| Operating Temperature | T <sub>A</sub>   | -40  | 25   | 85   | °C  |

## 2.3 DC CHARACTERISTICS

| Table4. | Control Signa | al Characteristics |

|---------|---------------|--------------------|

|---------|---------------|--------------------|

Test Condition: VDD =  $2.5V \pm 10\%$ , or  $3.3V \pm 10\%$ , TA = -40 to  $85^{\circ}$ C

| Donomotor                                       | Growbal          | Value |      |      | TT   | Community.                       |  |

|-------------------------------------------------|------------------|-------|------|------|------|----------------------------------|--|

| Parameter                                       | Symbol           | Min.  | Тур. | Max. | Unit | Comments                         |  |

| Core Supply<br>Current                          | I <sub>DD</sub>  |       | 12   | 25   | mA   | Enable 3 outputs                 |  |

| Output Buffer<br>Supply Current<br>(Per Output) | I <sub>DDO</sub> |       | 2    | 6    | mA   | $CLK0/1/2 \leq 100MHz, CL = 5pF$ |  |

https://www.dptel.com/

TEL:0086-0769-88010888

| Parameter           |           | Growbal         | Value |      |      | Unit | Comments                       |  |

|---------------------|-----------|-----------------|-------|------|------|------|--------------------------------|--|

|                     |           | Symbol          | Min.  | Тур. | Max. | Umt  | Comments                       |  |

| Input               | t Current | I <sub>IN</sub> |       |      | 10   | uA   | SDA, SCL                       |  |

| Output<br>Impedance |           | Zo              |       | 50   |      | Ω    | 3.3V VDDO, default high driver |  |

### 2.4 AC CHARACTERISTICS

| Table5. | AC Characteristics |

|---------|--------------------|

|---------|--------------------|

| Test Condition:  | VDD = 2.5V | + | 10% or $3.3V$  | + | 10%.  | $TA = -40$ to $85^{\circ}C$ |

|------------------|------------|---|----------------|---|-------|-----------------------------|

| rest contantion. | 100 2.01   |   | 10/0, 01 5.5 ( |   | 10/09 | 111 10 10 00 0              |

| D (                                 | G 1 1                     | Value                    |      |      | <b>T</b> T •4 | <b>C (</b>                                                            |

|-------------------------------------|---------------------------|--------------------------|------|------|---------------|-----------------------------------------------------------------------|

| Parameter                           | Symbol                    | Min.                     | Typ. | Max. | Unit          | Comments                                                              |

| Power-up Time                       | t <sub>RDY</sub>          |                          | 2    | 10   | ms            | From VDD = VDDMIN to valid<br>output clock, CL = 5pF, fCLKn ><br>1MHz |

| Power-up Time,<br>PLL Bypass Mode   | t <sub>BYP</sub>          |                          | 0.5  | 1    | ms            | From VDD = VDDMIN to valid<br>output clock, CL = 5pF, fCLKn ><br>1MHz |

| Output Frequency<br>Transition Time | t <sub>FREQ</sub>         |                          |      | 10   | us            | fCLKn > 1MHz                                                          |

| Output Phase<br>Offset              | P <sub>STEP</sub>         |                          | 333  |      | ps/step       |                                                                       |

| INPUT CLOCK C                       | HARACTI                   | ERISTIC                  | S    |      |               |                                                                       |

| Crystal Frequency                   | f <sub>XTAL</sub>         | 10                       | 27   | 40   | MHz           | $V_{CC}=3.3V, DP_R, DN_L = 1.5V, R_L$<br>= 50 $\Omega$                |

| Input Frequency                     | foscin                    | 2.8                      |      | 40   | MHz           | XA Single-Ended Input, XB floating                                    |

| OUTPUT CLOCK                        | CHARAC                    | TERIST                   | ICS  |      |               |                                                                       |

| Frequency<br>Range <sup>(1)</sup>   | F <sub>CLK</sub>          | 0.0025                   |      | 250  | MHz           |                                                                       |

| Load Capacitance                    | CL                        |                          |      | 15   | pF            |                                                                       |

|                                     |                           | 45                       | 50   | 55   | %             | FCLK $\leq$ 160MHz, measured at V <sub>DD</sub> /2                    |

| Duty Cycle                          | $t_{W/T}$                 | 40                       | 50   | 60   | %             | FCLK > 160MHz, measured at $V_{DD}/2$                                 |

| Dias/Eall Time                      | tr                        |                          | 1    | 1.5  | ns            | 20%~80%, CL = 5pF, Default high                                       |

| Rise/Fall Time                      | $t_{\rm f}$               |                          | 1    | 1.5  | ns            | drive strength                                                        |

| Output High<br>Voltage              | V <sub>OH</sub>           | V <sub>DD</sub> -<br>0.6 |      |      | V             | $C_L = 5pF$                                                           |

| Output Low<br>Voltage               | V <sub>OL</sub>           |                          |      | 0.6  | V             | $C_L = 5pF$                                                           |

| Period Jitter <sup>(2,3)</sup>      | $\mathbf{J}_{\text{PER}}$ |                          | 70   | 155  | ps            | Peak to peak, 3 outputs running                                       |

**INS8D5351A**

| Parameter                                 | Symbol            | Value            |      |      | Unit | Comments                        |

|-------------------------------------------|-------------------|------------------|------|------|------|---------------------------------|

| rarameter                                 | Symbol            | Min.             | Тур. | Max. | Umt  | Comments                        |

| Cycle-to-Cycle<br>Jitter <sup>(2,3)</sup> | J <sub>CC</sub>   |                  | 70   | 150  | ps   | Peak to peak, 3 outputs running |

| CRYSTAL REQU                              | REMENT            | S <sup>(4)</sup> |      |      |      |                                 |

| Crystal Frequency                         | f <sub>XTAL</sub> | 10               | 27   | 40   | MHz  |                                 |

| Load<br>Capacitance <sup>(4)</sup>        | $C_{\rm L}$       | 6                |      | 12   | pF   |                                 |

| Equivalent Series<br>Resistance           | ESR               |                  |      | 150  | Ω    | $\cdot$                         |

| Crystal Max Drive<br>Level                | $d_L$             | 100              |      |      | uW   |                                 |

\* Note:

(1) Only two unique frequencies above 112.5MHz can be simultaneously output.

(2) Measured over 10K cycles. Jitter is only specified at the default high drive strength (50 $\Omega$  output impedance).

(3) Jitter is highly dependent on device frequency configuration. Specifications represent a "worst case, real world" frequency plan; actual performance may be substantially better. Three-output 10 MSOP package measured with clock outputs of 74.25, 24.576 and 48MHz

4) Crystals which require load capacitances of 6, 8, or 10pF should use the device's internal load capacitance for optimum performance. See register 183 bits 7:6. A crystal with a 12pF load capacitance requirement should use a combination of the internal 10pF load capacitance in addition to external 2pF load capacitance (e.g., by using 4pF capacitors on XA and XB).

### 2.5 I<sup>2</sup>C SPECIFICATION

| Parameter                                                                            | Symbol                          | Standard mode<br>100Ksps   |                           | Fast mode<br>400Ksps |                            | Unit | Test Condition                                |

|--------------------------------------------------------------------------------------|---------------------------------|----------------------------|---------------------------|----------------------|----------------------------|------|-----------------------------------------------|

|                                                                                      |                                 | Min.                       | Max.                      | Min.                 | Max.                       |      |                                               |

| Low Level Input Voltage                                                              | V <sub>ILI2C</sub>              | -0.3                       | 0.3x<br>V <sub>DDI2</sub> | -0.3                 | 0.3x<br>V <sub>DDI2C</sub> | V    |                                               |

| High Level Input Voltage                                                             | V <sub>IHI2C</sub>              | 0.7x<br>V <sub>DDI2C</sub> | 3.6                       | 0.7x<br>Vddi2c       | 3.6                        | V    |                                               |

| Hysteresis of Schmitt<br>Trigger Inputs                                              | $V_{\rm HYS}$                   |                            |                           | 0.1                  |                            | V    |                                               |

| Low Level Output Voltage<br>(open drain or open<br>collector) at 3mA sink<br>current | V <sub>OLI2C</sub> <sup>1</sup> | 0                          | 0.4                       | 0                    | 0.4                        | V    | V <sub>DDI2C</sub> <sup>1</sup> =2.5/<br>3.3V |

| Input Current                                                                        | I <sub>II2C</sub>               | -10                        | 10                        | -10                  | 10                         | μΑ   |                                               |

| Capacitance for Each I/O Pin                                                         | C <sub>II2C</sub>               |                            | 4                         |                      | 4                          | pF   | $V_{IN}$ = -0.1 to<br>$V_{DDI2C}$             |

| I <sup>2</sup> C Bus Timeout                                                         | $T_{TO}$                        | 25                         | 35                        | 25                   | 35                         | mS   | Timeout<br>Enabled                            |

Table6. I<sup>2</sup>C Characteristics

TEL:0086-0769-88010888

https://www.dptel.com/

1) Note: Only I2C pull-up voltage (VDDI2C) of 2.25 to 3.6V are supported.

## 3. FUNCTIONAL DESCRIPTION

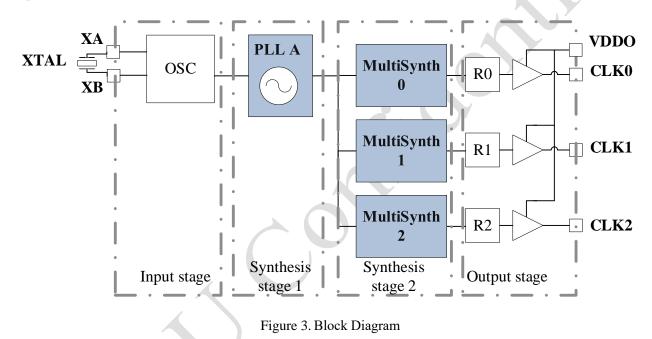

The INS8D5351A-GT is a versatile I2C programmable clock generator that is ideally suited for replacing crystals, crystal oscillators. A block diagram showing the general architecture of the INS8D5351A-GT is shown in Figure 3. The device consists of an input stage, two synthesis stages, and an output stage.

The input stage accepts an external crystal (XTAL) or a clock input (CLKIN). The first stage of synthesis is an integer-N PLL A which multiplies the input frequencies to a high-frequency intermediate clock A. The second stage uses high resolution MultiSynth fractional dividers to generate the desired output frequencies with low jitter. Additional integer division is provided at the output stage for generating output frequencies as low as 2.5 kHz.

### 3.1 Input Stage

### **Crystal Inputs (XA, XB)**

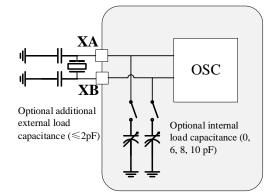

The INS8D5351A-GT uses a fixed-frequency standard AT-cut crystal as a reference to the internal oscillator. The output of the oscillator can be used to provide a free-running reference to the PLL A for generating asynchronous clocks. The output frequency of the oscillator will operate at the crystal frequency, from 10MHz to 40MHz. Internal load capacitors are provided to eliminate the need for external components when connecting a crystal to the INS8D5351A-GT. The total internal XTAL load capacitance (C<sub>L</sub>) can be selected to be 0, 6, 8, or 10pF. Crystals with alternate load capacitance requirements are supported using additional external load capacitance  $\leq 2pF$  (e.g., by using  $\leq 4pF$  capacitors on XA and XB) as shown in Figure 4.

Figure 4. External XTAL with Optional Load Capacitors

### **External Clock Input**

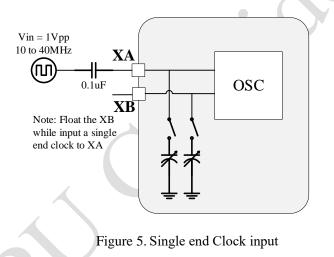

The INS8D5351A-GT can be driven with a clock signal through the XA input pin. This is especially useful when in need of generating clock outputs in two synchronization domains. With the INS8D5351A-GT, one reference clock can be provided at XA as shown in figure 5. The external clock input from 10 to 40MHz is used as a clock reference for the PLL A when generating synchronous clock outputs.

### 3.2 Synthesis Stages

The INS8D5351A-GT uses two stages of synthesis to generate its final output clocks. The stage 1 uses PLL A to multiply the lower frequency input reference to a high-frequency intermediate clock. The stage 2 uses high resolution MultiSynth fractional dividers to generate the required output frequencies. Only two unique frequencies above 112.5MHz can be simultaneously output.

### 3.3 Output Stage

An additional level of division (R) is available at the output stage for generating clocks as low as 2.5 kHz. All output drivers generate CMOS level outputs with separate output voltage supply pins (VDDO) allowing a different voltage signal level (1.8, 2.5, or 3.3 V).

#### **CONFIGURING THE INS8D5351A-GT** 4.

The INS8D5351A-GT is a highly flexible clock generator which is entirely configurable through its I2C interface.

### 4.1 I2C Bus Interface

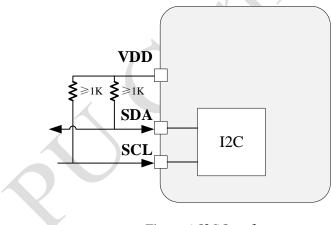

The I2C interface operates in slave mode with 7-bit addressing and can operate in Standard-Mode (100 kbps) or Fast-Mode (400 kbps) and supports burst data transfer with auto address increments.

The I2C bus consists of a bidirectional serial data line (SDA) and a serial clock input (SCL) as shown in Figure 6. Both the SDA and SCL pins must be connected to the VDD supply via an external pull-up as recommended by the I2C specification.

Figure 6. I2C Interface

#### **Slave Address** 4.1.1

The 7-bit device (slave) address of the INS8D5351A-GT consist of a 6-bit fixed address plus a user selectable LSB bit as shown in Table 7. The LSB bit is selectable as 0 or 1 using the optional A0 pin which is useful for applications that require more than one INS8D5351A-GT on a single I2C bus.

| ADDR  | Transfer data |      | Slave address |      |      |      |      |      |           |

|-------|---------------|------|---------------|------|------|------|------|------|-----------|

| ADDK  |               | bit7 | bit6          | bit5 | bit4 | bit3 | bit2 | bit1 | bit0      |

| Low   | 61h (Read)    | 1    | 1             | 0    | 0    | 0    | 0    | 0    | 1 (Read)  |

| Level | C0h (Write)   | 1    | 1             | 0    | 0    | 0    | 0    | 0    | 0 (Write) |

|       | C3h (Read)    | 1    | 1             | 0    | 0    | 0    | 0    | 1    | 1 (Read)  |

https://www.dptel.com/

| Table7. I <sup>2</sup> C Bus Slave | Address |

|------------------------------------|---------|

|------------------------------------|---------|

TEL:0086-0769-88010888

| ADDR | Transfer data | Slave address |      |      |      |      |      |      | R/W       |

|------|---------------|---------------|------|------|------|------|------|------|-----------|

|      |               | bit7          | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0      |

| High | C2h (Write)   | 1             | 1    | 0    | 0    | 0    | 0    | 1    | 0 (Write) |

INS8D5351A-GT I<sup>2</sup>C bus Slave Address is [1100 00\*].

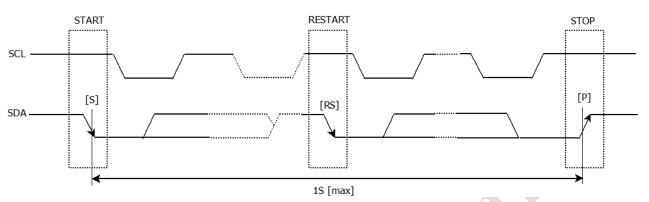

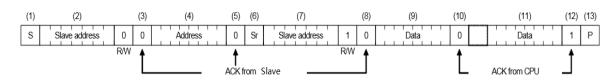

### 4.1.2 I2C bus protocol

It is assumed CPU is master and INS8D5351A-GT is slave in this section.

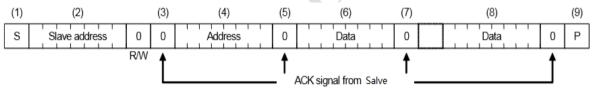

### Write process

I<sup>2</sup>C bus includes an address auto-increment function, once the initial address has been specified, the INS8D5351A-GT increments (+1) the address automatically after each data is sent, then to write next data.

- (1) CPU sends start condition[S]

- (2) CPU sends INS8D5351A-GT 's slave address with R/W bit to be set to write mode

- (3) CPU verifies ACK signal from INS8D5351A-GT

- (4) CPU sends write register address to INS8D5351A-GT

- (5) CPU verifies ACK signal from INS8D5351A-GT

- (6) CPU sends write data to the address specified at step (4)

- (7) CPU verifies ACK signal from INS8D5351A-GT

- (8) Repeat (6) (7) if multiple bytes need to be written, address will be incremented automatically

- (9) CPU ends stop condition[P]

### Read process

There are two cases for read process.

Case 1: Setting the register address for reading from INS8D5351A-GT

- (1) CPU sends start condition[S]

- (2) CPU sends INS8D5351A-GT 's slave address with R/W bit to be set to write mode

- (3) CPU verifies ACK signal from INS8D5351A-GT

- (4) CPU sends register address for reading from INS8D5351A-GT

- (5) CPU verifies ACK signal from INS8D5351A-GT

- (6) CPU sends RESTART condition [Sr]

- (7) CPU sends INS8D5351A-GT 's slave address with R/W bit to be set to read mode

- (8) CPU verifies ACK signal from INS8D5351A-GT

- (9) CPU reads data from the specified address in step (4)

- (10)CPU sends ACK signal to INS8D5351A-GT

- (11)Repeat (9) (10) if multiple bytes need to be read, address will be incremented automatically

- (12)CPU sends ACK signal for "1" to INS8D5351A-GT

- (13)CPU sends stop condition[P]

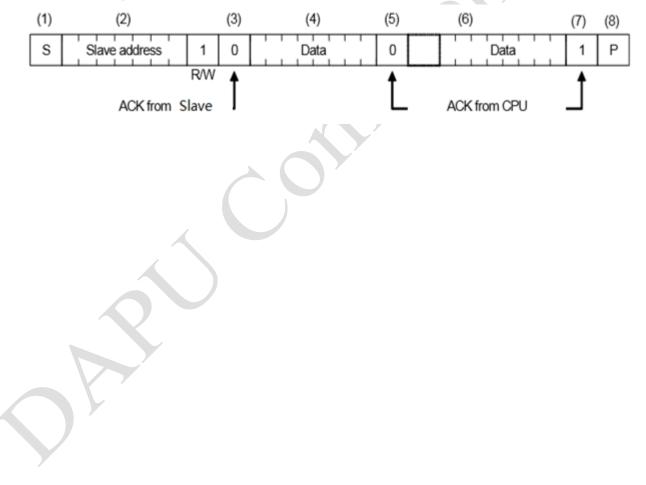

Case 2: Writing the slave address to be read with read mode directly and without register address setting.

- (1) CPU sends START condition [S]

- (2) CPU sends INS8D5351A-GT 's slave address with R/W bit to be set to read mode

- (3) CPU verifies ACK signal from INS8D5351A-GT

- (4) CPU reads data from the latest register address which is updated by the last write data process or read data process

- (5) CPU sends ACK signal to INS8D5351A-GT

- (6) Repeat (9) (10) if multiple bytes need to be read, address will be incremented automatically

- (7) CPU sends ACK signal for "1" to INS8D5351A-GT

- (8) CPU sends stop condition[P]

# INS8D5351A

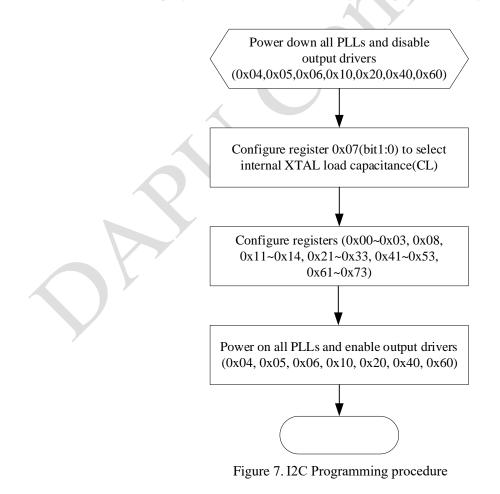

### 4.2 Write a Custom Configuration to RAM

Many of the functions and features of the INS8D5351A-GT are controlled by reading and writing to the RAM space using the I2C interface. The following is a list of the common features that are controllable through the I2C interface.

Read Status Indicators:

- Crystal Reference Loss of signal, LOS\_XTAL, reg0[3]

- PLL A and/or MultiSynth Loss of lock, LOL\_M or LOL\_S, reg0[6:5]

- Configuration of multiplication and divider values for the PLLs, dividers

- Set output clock options

- Enable/disable for each clock output

- Invert/non-invert for each clock output

- Output divider values (2n, n=1...7)

- Output state when disabled (stop Hi, stop Low, Hi-Z)

- Output phase offset

INS8D5351A-GT can be programmed via I2C by following the steps shown in Figure 7. Refer to "Appendix-1:

## 5. TYPICAL APPLICATION

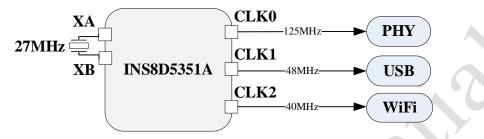

### 5.1 INS8D5351A-GT replaces Multiple Clocks and XOs

The INS8D5351A-GT is a user-definable custom clock generator that is ideally suited for replacing crystals and crystal oscillators in cost-sensitive applications. An example application is shown in figure 8.

Figure 8. Using INS8D5351A-GT to replace multiple crystals, crystal oscillators

### 5.2 HCSL Compatible Outputs

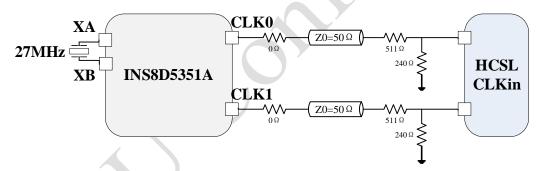

The INS8D5351A-GT can be configured to support HCSL compatible swing when the VDDO of the output power supply is set to 2.5 V.

The circuit in the figure 9 below must be applied to each of the two clocks used, and one of the clocks in the pair must also be inverted to generate a differential pair. See register setting CLKx\_INV.

Figure 9. INS8D5351A-GT Output is HCSL compatible

## 6. DESIGN CONSIDERATIONS

The INS8D5351A-GT is a self-contained clock generator that requires very few external components. The following general guidelines are recommended to ensure optimum performance.

### 6.1 Power Supply Decoupling/Filtering

The INS8D5351A-GT has built-in power supply filtering circuitry and extensive internal Low Drop Out (LDO) voltage regulators to help minimize the number of external bypass components. All that is recommended is one 0.1 to 1.0  $\mu$ F decoupling capacitor per power supply pin. This capacitor should be mounted as close to the VDD and VDDO pins as possible without using vias.

### 6.2 Power Supply Sequence

The VDD and VDDO power supply pins have been separated to allow flexibility in output signal levels. Power supply sequencing for VDD and VDDO requires that all VDDO be powered up either before or at the same time as VDD.

### 6.3 External Crystal

The external crystal should be mounted as close to the pins as possible using short PCB traces. The XA and XB traces should be kept away from other high-speed signal traces.

### 6.4 External Crystal Load Capacitors

The INS8D5351A-GT provides the option of using internal and external crystal load capacitors. If internal load capacitance is insufficient, capacitors of value less than 2pF may be used to increased equivalent load capacitance. If external load capacitors are used, they should be placed as close to the XA/XB pads as possible.

### 6.5 Unused Pins

Unused XB pins should be left floating. Unused output pins (CLK0~CLK2) should be left floating.

### 6.6 Trace Characteristics

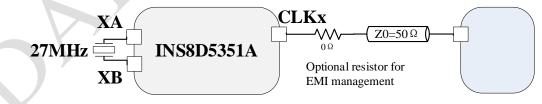

The INS8D5351A-GT features various output current drive strengths. It is recommended to configure the trace characteristics as shown in figure 10 when the default high drive strength is used.

Figure 10. Recommended trace characteristics with default drive strength setting

TEL:0086-0769-88010888

https://www.dptel.com/

**INS8D5351A**

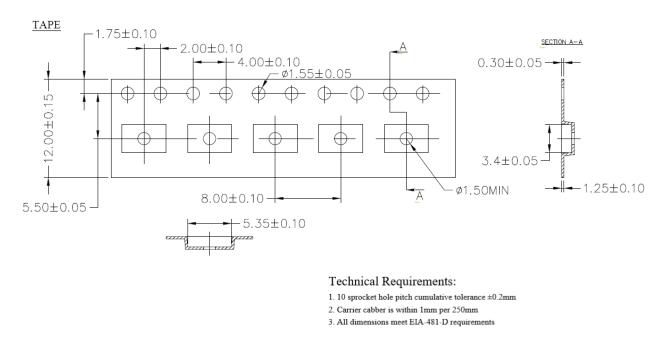

## 7. Mechanical Structure (mm)

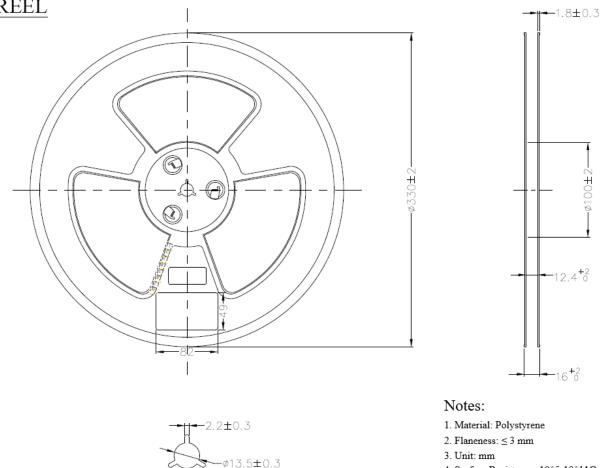

## TAPE AND REEL INFORMATION(MSOP10)

- 4. Surface Resistance: 10^5-10^11 $\Omega$

- 5. Unmarked tolerance: ±0.25

## Appendix-1

Refer to "AN5351-1: Manually Generating an INS8D5351A-GT Register Map" for a detailed description of INS8D5351A-GT registers.