# DAP8211R — Gigabit Ethernet PHY

#### Overview

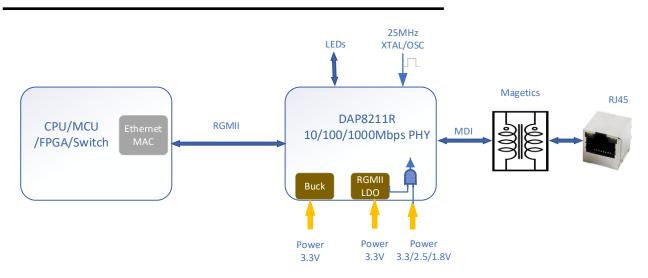

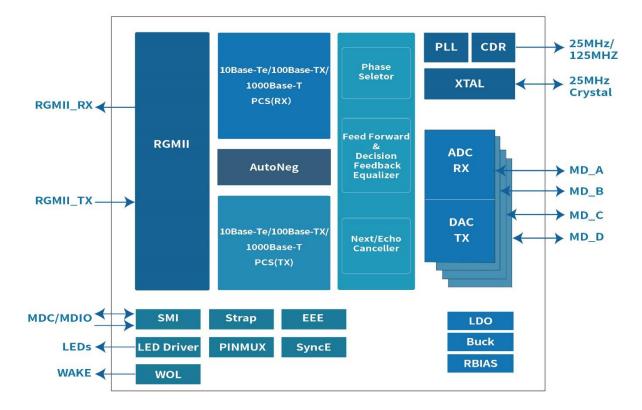

The DAP8211R device is a robust, low power, single port Gigabit Ethernet and fully featured Physical Layer transceiver which is compliant with IEEE802.3 10BASE-Te, IEEE802.3u 100BASE-TX and IEEE802.3ab 1000BASE-T Ethernet protocols.

DAPL

This device interfaces directly to the MAC layer through RGMII (Reduced GMII). It supports RGMII to Copper.

The DAP8211R is designed for easy implementation of 10/100/1000 Mbps Ethernet LANs. The MDI ports interfaces directly to twisted pair media through the external transformer.

Additionally, the DAP8211R provides precision clock synchronization, including a synchronous Ethernet clock output.

The DAP8211R supports single 3.3V power supply and configurable RGMII I/O voltage supporting 3.3V, 2.5V and 1.8V.

Designed for low power, EEE and Wake-on-LAN can be used to lower system power consumption.

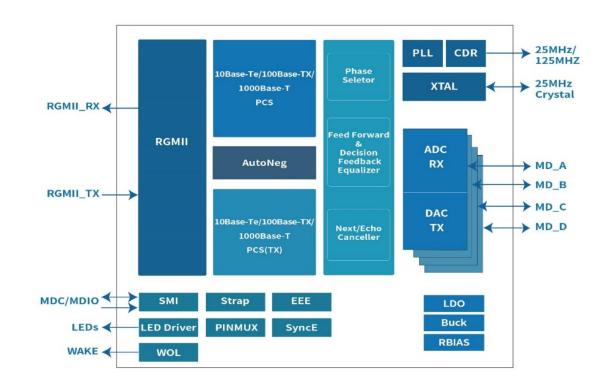

### **Block Diagram**

# **Key Features**

- RGMII MAC interface

- 1000BASE-T IEEE 802.3ab /100BASE-TX

IEEE 802.3u/10BASE-Te IEEE 802.3 Compliant

- EEE(IEEE 802.3az-2010)

- Supports SyncE

- WoL (Wake-on-LAN)

- Sleep Mode

- Crossover Detection & Auto-Correction

- Supports Parallel Detection

- Supports Base Line Wander Correction

- Supports Interrupt function

- Automatic polarity correction

- Integrate Linear/Buck Switching Regulator

- 120 meters at 1000Mbps over CAT.5E cable

- Configurable I/O voltage (3.3 V, 2.5 V, 1.8 V) signaling for RGMII

- 3.3V single power supply

- 3 LEDs for Network Status

- 25MHz external crystal/oscillator

- Output 25MHz/125MHz clock for MAC

- Operation Temperature Range:  $0^{\circ}C \sim +70^{\circ}C$

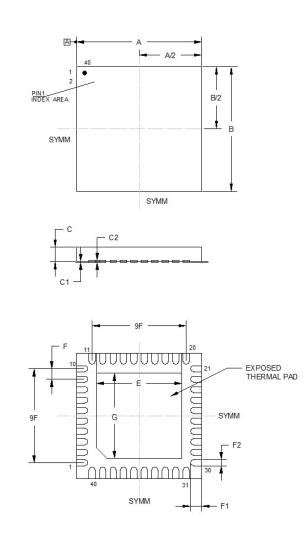

- Package: QFN 40-pin (5mm x 5mm)

# Applications

- Enterprise & SOHO

- Wireless Router

- Industrial controls and automation

- LED Display

- Motor drives

- Industrial factory automation

- Field Bus Support

- Industrial embedded computing

- Wired and wireless communications infrastructure

- Test and measurement

- Consumer electronics

Songshan Lake · Dongguan · Guangdong

# **Applications Diagram**

# **Revision History**

| Revision | Change Contents       | Prepared by | Revised Date |

|----------|-----------------------|-------------|--------------|

| V1.0     | First Issued          |             | 2022.2.14    |

| V1.1     | Update the dimensions |             | 2022.2.22    |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

|          |                       |             |              |

Songshan Lake · Dongguan · Guangdong

# Index

| C | )VE | RV   | IEW.    |                              | 1  |

|---|-----|------|---------|------------------------------|----|

| B | LO  | СК   | DIA     | GRAM                         | 1  |

| K | ΈY  | FE   | ATUI    | RES                          | 2  |

| A | PPI | LIC  | ATIO    | NS                           | 2  |

| A | PPI | LIC  | ATIO    | NS DIAGRAM                   | 3  |

| R | EV  | ISIO | ON H    | ISTORY                       | 4  |

| Π | NDF | EX.  |         |                              | 5  |

| 1 |     | PI   | N DEF   | INITION                      | 10 |

|   | 1.1 | 1    | OFN4    | 10 Pin Assignments           | 10 |

| 2 |     | EL   | -       | CAL CHARACTERISTICS          |    |

| - | 2.1 |      |         | LUTE MAXIMUM RATINGS         |    |

|   | 2.2 |      |         | MMENDED OPERATING CONDITIONS |    |

|   | 2.3 |      |         | HARACTERISTICS               |    |

|   | 2.3 |      |         | CHARACTERISTICS              |    |

|   |     | -    |         |                              |    |

|   | 2.5 |      |         | G CHARACTERISTICS            |    |

|   |     | 2.5  |         | Reset Timing                 |    |

|   |     | 2.5  | .2      | RGMII Interface Timing       |    |

|   |     | 2.5  | .3      | SMI Interface Timing         | 18 |

| 3 |     | DE   | ETAIL I | DESCRIPTION                  | 19 |

|   | 3.1 | 1    | BLOCK   | ( DIAGRAM                    | 19 |

|   | 3.2 | 2    | Featu   | IRE DESCRIPTION              | 19 |

|   |     | 3.2  | .1      | WoL (Wake-on-LAN)            | 19 |

|   |     | 3.2  | .2      | IEEE 802.3az-2010 (EEE)      | 20 |

|   |     | 3.2  | .3      | SyncE                        | 20 |

|   |     | 3.2  | .4      | nINT/nPME                    | 20 |

TEL:0086-0769-88010888

https://www.dptel.com/

4

# Guangdong Dapu Telecom Technology Co., Ltd

|     | 3.2.5                                                                                    | MDI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                       |

|-----|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|     | 3.2.6                                                                                    | MAC Interface(RGMII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                       |

|     | 3.2.7                                                                                    | Management Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                       |

|     | 3.2.8                                                                                    | Loopback Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                       |

|     | 3.2.9                                                                                    | Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21                                                       |

|     | 3.2.10                                                                                   | Auto-Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                       |

|     | 3.2.11                                                                                   | Crossover Detection and Auto-Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                       |

|     | 3.2.12                                                                                   | Baseline Wander Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                       |

|     | 3.2.13                                                                                   | Echo Cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23                                                       |

|     | 3.2.14                                                                                   | Crosstalk Cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                       |

|     | 3.2.15                                                                                   | LED Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                       |

|     | 3.2.16                                                                                   | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                       |

|     | 3.2.17                                                                                   | Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                       |

|     | 3.2.18                                                                                   | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24                                                       |

|     |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|     | 3.2.19                                                                                   | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                       |

|     |                                                                                          | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

| 4.1 | REGISTE                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                       |

| 4.1 | REGISTE                                                                                  | RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b> 25</b><br>25                                         |

| 4.1 | <b>REGISTE</b><br>BASIC                                                                  | REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b> 25</b><br>25<br>26                                   |

| 4.1 | REGISTE<br>BASIC<br>4.1.1                                                                | RS<br>REGISTER<br>BMCR(Basic Mode Control , Address: Register 0)                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b> 25</b><br>25<br>26<br>27                             |

| 4.1 | <b>REGISTE</b><br>BASIC<br>4.1.1<br>4.1.2                                                | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)                                                                                                                                                                                                                                                                                                                                                                                         | <b> 25</b><br>25<br>26<br>27<br>29                       |

| 4.1 | <b>REGISTE</b><br>BASIC<br>4.1.1<br>4.1.2<br>4.1.3                                       | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)<br>PHYID1 (PHY Identifier Register #1, Address: Register 2)                                                                                                                                                                                                                                                                                                                             | 25<br>25<br>26<br>27<br>29<br>29                         |

| 4.1 | <b>REGISTE</b><br>BASIC<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                              | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)<br>PHYID1 (PHY Identifier Register #1, Address: Register 2)<br>PHYID2 (PHY Identifier Register #2, Address : Register 3)                                                                                                                                                                                                                                                                | 25<br>25<br>26<br>27<br>29<br>29<br>29                   |

| 4.1 | REGISTE<br>BASIC<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                            | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)<br>PHYID1 (PHY Identifier Register #1, Address: Register 2)<br>PHYID2 (PHY Identifier Register #2, Address: Register 3)<br>ANAR (Auto-Negotiation Advertising, Address: Register 4)                                                                                                                                                                                                     | 25<br>25<br>26<br>27<br>29<br>29<br>29<br>30             |

| 4.1 | REGISTE<br>BASIC<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6                   | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)<br>PHYID1 (PHY Identifier Register #1, Address: Register 2)<br>PHYID2 (PHY Identifier Register #2, Address: Register 3)<br>ANAR (Auto-Negotiation Advertising, Address: Register 4)<br>ANLPA (Auto-Negotiation Link Partner Ability, Address: Register 5)                                                                                                                               | 25<br>25<br>26<br>27<br>29<br>29<br>29<br>30<br>31       |

| 4.1 | REGISTE<br>BASIC<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7          | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)<br>PHYID1 (PHY Identifier Register #1, Address: Register 2)<br>PHYID2 (PHY Identifier Register #2, Address: Register 3)<br>ANAR (Auto-Negotiation Advertising, Address: Register 4)<br>ANLPA (Auto-Negotiation Link Partner Ability, Address: Register 5)<br>ANE (Auto-Negotiation Expansion Address: Register 6)                                                                       | 25<br>25<br>26<br>27<br>29<br>29<br>29<br>30<br>31<br>32 |

| 4.1 | REGISTE<br>BASIC<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8 | RS<br>REGISTER<br>BMCR(Basic Mode Control, Address: Register 0)<br>BMSR (Basic Mode Status, Address: Register 1)<br>PHYID1 (PHY Identifier Register #1, Address: Register 2)<br>PHYID2 (PHY Identifier Register #2, Address : Register 3)<br>ANAR (Auto-Negotiation Advertising, Address: Register 4)<br>ANLPA (Auto-Negotiation Link Partner Ability, Address: Register 5)<br>ANE (Auto-Negotiation Expansion Address: Register 6)<br>ANNPT (Auto-Negotiation Next Page Transmit Address: Register 0x7) | 25<br>25<br>26<br>27<br>29<br>29<br>30<br>31<br>32<br>32 |

| 4.1.12  | MMD_AC (MMD Access Control; Address: Register 0xD)                   |  |

|---------|----------------------------------------------------------------------|--|

| 4.1.13  | MMD_AAD (MMD Access Address Data, Address: Register 0xE)             |  |

| 4.1.14  | 1000BTS (1000BASE-T Status Register, Address: Register 0xF)          |  |

| 4.1.15  | PHYCR (PHY Control Register, Address: Register 0x10)                 |  |

| 4.1.16  | PHYSR (PHY Status Register, Address: Register 0x11)                  |  |

| 4.1.17  | INTCR (Interrupt Control Register, Address: Register 0x12)           |  |

| 4.1.18  | INTSR (Interrupt Status Register, Address: Register 0x13)            |  |

| 4.1.19  | SPCR (Speed Configuration Register, Address: Register 0x14)          |  |

| 4.1.20  | RECR (Receiver Error Counter Register, Address: Register 0x15)       |  |

| 4.1.21  | EXT_ADD (Extended Register Address Register, Address: Register 0x1E) |  |

| 4.1.22  | EXT_DATA (Extended Register Data Register, Register 0x1F)            |  |

| 4.2 PAC | KAGE GENERATION EXTENDED REGISTER                                    |  |

| 4.2.1   | PKGC1 (Package Generation Configure1, Address: Register 0x38)        |  |

| 4.2.2   | PKGC2(Package Generation Configure2, Address: Register 0x39)         |  |

| 4.2.3   | PKGC3(Package Generation Configure3, Address: Register 0x3A)         |  |

| 4.2.4   | PKGC4(Package Generation Configure4, Address: Register 0x3B)         |  |

| 4.2.5   | PKGC5 (Package Generation Configure5, Address: Register 0xA0)        |  |

| 4.2.6   | PKGC6(Package Generation Configure6, Address: Register 0xA1)         |  |

| 4.2.7   | PKGC7(Package Generation Configure7, Address: Register 0xA2)         |  |

| 4.2.8   | PKG_RV_H(Package Receiver Valid High, Address: Register 0xA3)        |  |

| 4.2.9   | PKG_RV_L(Package Receiver Valid Low, Address: Register 0xA4)         |  |

| 4.2.10  | PKG_RX_OSH(Package Receiver OS High, Address: Register 0xA5)         |  |

| 4.2.11  | PKG_RX_OSL(Package Receiver OS Low, Address: Register 0xA6)          |  |

| 4.2.12  | PKG_RX_USH(Package Receiver US High, Address: Register 0xA7)         |  |

| 4.2.13  | PKG_RX_USL(Package Receiver US Low, Address: Register 0xA8)          |  |

| 4.2.14  | PKG_RX_ERR(Package Receiver Error, Address: Register 0xA9)           |  |

| 4.2.15  | PKG_RX_OS_ERR(Package Receiver OS Error, Address: Register 0xAA)     |  |

| 4.2.16  | PKG_RX_FRM (Package Receiver Fragment, Address: Register 0xAB)       |  |

|         |                                                                      |  |

| 4.2.17  | PKG_RX_NOSFD (Package Receiver NOSFD, Address: Register 0xAC)            | 43 |

|---------|--------------------------------------------------------------------------|----|

| 4.2.18  | PKG_TV_H(Package Transmit Valid High, Address: Register 0xAD)            | 43 |

| 4.2.19  | PKG_TV_L(Package Transmit Valid Low, Address: Register 0xAE)             | 43 |

| 4.2.20  | PKG_TX_OSH(Package Transmit OS High, Address: Register 0xAF)             | 44 |

| 4.2.21  | PKG_TX_OSL(Package Transmit OS Low, Address: Register 0xB0)              | 44 |

| 4.2.22  | PKG_TX_USH(Package Transmit US High, Address: Register 0xB1)             | 44 |

| 4.2.23  | PKG_TX_USL(Package Transmit US Low, Address: Register 0xB2)              | 44 |

| 4.2.24  | PKG_TX_ERR(Package Transmit Error, Address: Register 0xB3)               | 44 |

| 4.2.25  | PKG_TX_OS_ERR(Package Transmit OS Error, Address: Register 0xB4)         | 44 |

| 4.2.26  | PKG_TX_FRM (Package Transmit Fragment, Address: Register 0xB5)           | 45 |

| 4.2.27  | PKG_TX_NOSFD (Package Transmit NOSFD, Address: Register 0xB6)            | 45 |

| 4.3 Gen | ERAL EXTENDED REGISTER                                                   | 45 |

| 4.3.1   | PHY_CON (PHY Device Control Register, Address: Register 0xA001)          | 45 |

| 4.3.2   | RGMII_CON (RGMII Control Register, Address: Register 0xA003)             | 46 |

| 4.3.3   | RGMII_STA (RGMII Status Register, Address: Register 0xA004)              | 46 |

| 4.3.4   | SMI_RGMII_CON (SMI & RGMII Control Register, Address: Register 0xA005)   | 46 |

| 4.3.5   | MISC_CON (MISC Control Register, Address: Register 0xA006)               | 47 |

| 4.3.6   | WOL_MAC_ADDH(WOL MAC Highest Address Register, Address: Register 0xA007) | 47 |

| 4.3.7   | WOL_MAC_ADDM(WOL MAC Middle Address Register, Address: Register 0xA008)  | 47 |

| 4.3.8   | WOL_MAC_ADDL(WOL MAC Lowest Address Register, Address: Register 0xA009)  | 48 |

| 4.3.9   | WOL_CON (WOL Control Register, Address: Register 0xA00A)                 | 48 |

| 4.3.10  | LED_COMCON (LED Common Control Register, Address: Register 0xA00B)       |    |

| 4.3.11  | LED0_CON (LED0 Control Register, Address: Register 0xA00C)               | 49 |

| 4.3.12  | LED1_CON (LED1 Control Register, Address: Register 0xA00D)               | 50 |

| 4.3.13  | LED2_CON (LED2 Control Register, Address: Register 0xA00E)               | 51 |

| 4.3.14  | LED_BLCON (LED Blink Control Register, Address: Register 0xA00F)         | 52 |

| 4.3.15  | DRV_STR (Driver Strength Control Register, Address: Register 0xA010)     | 53 |

| 4.3.16  | SyncE_CON (SyncE Control Register, Address: Register 0xA012)             | 53 |

|         |                                                                          |    |

|   | 4.4 | MMD    | DExtended Register                                                 | 54 |

|---|-----|--------|--------------------------------------------------------------------|----|

|   | 4.  | .4.1   | PCS_CON (PCS Control Register, Address: MMD3 Register 0x00)        | 54 |

|   | 4.  | .4.2   | PCS_STA (PCS Status Register, Address: MMD3 Register 0x01)         | 54 |

|   | 4.  | .4.3   | EEE_CON (EEE Control Register, Address: MMD3 Register 0x14)        | 55 |

|   | 4.  | .4.4   | EEE_WERR (EEE Wake Error Register, Address: MMD3 Register 0x16)    | 55 |

|   | 4.  | 4.5    | EEE_LA (EEE Local Ability Register, Address: MMD7 Register 0x3C)   | 55 |

|   | 4.  | .4.6   | EEE_PA (EEE Partner Ability Register, Address: MMD7 Register 0x3D) | 56 |

| 5 | E   | INVIRO | NMENT                                                              | 57 |

| 6 | [   | DIMENS | SIONS                                                              | 58 |

|   | 6.1 | OFN4   | 10 DIMENSIONS                                                      | 58 |

Songshan Lake · Dongguan · Guangdong

1 Pin Definition

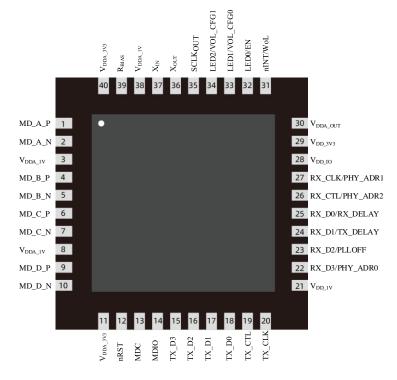

# 1.1 QFN40 Pin Assignments

Figure 1 Package 40-Pin (Top View)

- I: Input Signal

- O: Output Signal

- PWR: Power Supply

- GND: Ground

- EPAD: Exposed thermal PAD

Table1. Pin Definition

| Pin<br>Number | Pin Name            | I/O | Description                                                                               |

|---------------|---------------------|-----|-------------------------------------------------------------------------------------------|

| POWER AN      | D GROUND            |     |                                                                                           |

| 11, 40        | VDDA_3V3            | PWR | 3.3V Analog Supply. A $1\mu$ F and $0.1\mu$ F capacitor are required to GND for each pin. |

| 3, 8, 38      | V <sub>DDA_1V</sub> | PWR | 1.1V/1.2V Analog Supply. A 1µF and $0.1µF$ capacitor are required to GND for each pin.    |

| 21            | $V_{DD_1V}$         | PWR | Digital Core Power. 1.1V/1.2V                                                             |

| 28            | $V_{DD_{-IO}}$      | PWR | Digital I/O power input for RGMII I/O, MDC/MDIO                                           |

Songshan Lake · Dongguan · Guangdong

DAPU

|           |                     |        | If disabled the internal LDO, $V_{DD_{-IO}}$ should be supplied by the external power supply.                                                                                                                                              |  |  |

|-----------|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           |                     |        | This pin need a bulk capacitor and a decoupling capacitor.                                                                                                                                                                                 |  |  |

| 29        | V <sub>DD_3V3</sub> | PWR    | 3.3V Digital power input for others IO excluding RGMII, MDIO                                                                                                                                                                               |  |  |

| 30        | Vdda_out            | PWR_O  | For DAP8211R, Regulator power output 1.1V. A 2.2µH inductor is required.                                                                                                                                                                   |  |  |

| 41        | EPAD                | GND    | Exposed PAD Ground                                                                                                                                                                                                                         |  |  |

| CLOCK     |                     |        |                                                                                                                                                                                                                                            |  |  |

| 35        | SCLK <sub>OUT</sub> | О      | <ul> <li>25/125MHz Clock Output.</li> <li>Reference Clock Generated from Internal PLL</li> <li>Recovered clock from UTP for SyncE.</li> </ul>                                                                                              |  |  |

|           |                     |        | • Synchronized with the 25 MHz reference clock                                                                                                                                                                                             |  |  |

| 36        | Xout                | 0      | Crystal Output: 25-MHz crystal output<br>If external oscillator provides clock to X <sub>IN</sub> , the X <sub>OUT</sub> must be floating.<br>If external oscillator provides clock to X <sub>OUT</sub> , the X <sub>IN</sub> must be GND. |  |  |

| 37        | X <sub>IN</sub>     | Ι      | Crystal Input: 25-MHz crystal input<br>If external oscillator provides clock to X <sub>IN</sub> , the X <sub>OUT</sub> must be floating.<br>If external oscillator provides clock to X <sub>OUT</sub> , the X <sub>IN</sub> must be GND.   |  |  |

| MEDIA DEP | PENDENT INTERFACE   | 1      |                                                                                                                                                                                                                                            |  |  |

| 1         | MD_A_P              | I/O    | Media Dependent Interface, Differential Transmit and Receive 1st Signals                                                                                                                                                                   |  |  |

| 2         | MD_A_N              | I/O    | Media Dependent Interface, Differential Transmit and Receive 1 <sup>st</sup> Signals                                                                                                                                                       |  |  |

| 4         | MD_B_P              | I/O    | Media Dependent Interface, Differential Transmit and Receive 2 <sup>nd</sup> Signals                                                                                                                                                       |  |  |

| 5         | MD_B_N              | I/O    | Media Dependent Interface, Differential Transmit and Receive 2 <sup>nd</sup> Signals                                                                                                                                                       |  |  |

| 6         | MD_C_P              | I/O    | Media Dependent Interface, Differential Transmit and Receive 3rd Signals                                                                                                                                                                   |  |  |

| 7         | MD_C_N              | I/O    | Media Dependent Interface, Differential Transmit and Receive 3rd Signals                                                                                                                                                                   |  |  |

| 9         | MD_D_P              | I/O    | Media Dependent Interface, Differential Transmit and Receive 4 <sup>th</sup> Signals                                                                                                                                                       |  |  |

| 10        | MD_D_N              | I/O    | Media Dependent Interface, Differential Transmit and Receive 4 <sup>th</sup> Signals                                                                                                                                                       |  |  |

| MANAGEM   | ENT INTERFACE       |        |                                                                                                                                                                                                                                            |  |  |

| 12        | nRST                | Ι      | Reset: The active low RESET initializes or reinitializes the PHY. All internal registers reinitialize to the default state after reset.<br>Note: The reset signal must be held low at least 10 ms, suggest to be pulled up.                |  |  |

| 13        | MDC                 | I/PD   | Management Data Clock                                                                                                                                                                                                                      |  |  |

| 14        | MDIO                | I/O/PU | Input/Output of Management Data.                                                                                                                                                                                                           |  |  |

| 31        | nINT/nPME           | O/OD   | <ul> <li>This pin is shared by two functions, keep this pin floating if either of the functions is not used.</li> <li>1. Interrupt (supports 3.3V pull up).</li> <li>Set low if the specified events happened; active low.</li> </ul>      |  |  |

Songshan Lake · Dongguan · Guangdong

DAPU

|                    |                  |          | <ul><li>2. Power Management Event (supports 3.3V pull up).</li><li>Set low if received a magic packet or Wake-Up frame, or wake up event; active low.</li></ul> |  |

|--------------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>RGMII</b> Inter | rface            |          |                                                                                                                                                                 |  |

| 15                 | TX_D3            | I/PD     | RGMII Transmit Data. Data is transmitted from MAC to PHY                                                                                                        |  |

| 16                 | TX_D2            | I/PD     | RGMII Transmit Data. Data is transmitted from MAC to PHY                                                                                                        |  |

| 17                 | TX_D1            | I/PD     | RGMII Transmit Data. Data is transmitted from MAC to PHY                                                                                                        |  |

| 18                 | TX_D0            | I/PD     | RGMII Transmit Data. Data is transmitted from MAC to PHY                                                                                                        |  |

| 19                 | TX_CTL           | I/PD     | RGMII Transmit Control Signal                                                                                                                                   |  |

| 20                 | TX_CLK           | I/PD     | RGMII Transmit Reference Clock, 125Mhz, 25MHz, or 2.5MHz                                                                                                        |  |

| 22                 | RX_D3/PHY_ADR0   | O/LI/PD  | RGMII Receiver Data. Data is transmitted from PHY to MAC.                                                                                                       |  |

|                    |                  |          | PHY Address[0]                                                                                                                                                  |  |

| 23                 | RX_D2/PLLOFF     | O/LI/PD  | RGMII Receiver Data. Data is transmitted from PHY to MAC.                                                                                                       |  |

|                    |                  | 0/20/10  | In sleep mode, PLL off configuration when pulled down.                                                                                                          |  |

|                    | RX_D1/TX_DELAY   |          | RGMII Receiver Data. Data is transmitted from PHY to MAC.                                                                                                       |  |

| 24                 |                  | O/LI/PD  | RGMII transmit timing delay control. Pull up to add 2ns delay to TXC for                                                                                        |  |

|                    |                  |          | TXD latching for 125MHz TX_CLK.                                                                                                                                 |  |

|                    |                  |          | RGMII Receiver Data. Data is transmitted from PHY to MAC.                                                                                                       |  |

|                    |                  |          | RGMII receive timing delay control.                                                                                                                             |  |

| 25                 | RX_D0/RX_DELAY   | O/LI/PU  | Pull-up to add: 2ns delay on RX_CLK when RX_CLK is 125MHz                                                                                                       |  |

|                    |                  |          | Or 8ns delay on RX_CLK when RX_CLK is 25MHz/2.5MHz,                                                                                                             |  |

|                    |                  |          | which shall be used to latch RXD.                                                                                                                               |  |

| 26                 | RX_CTL/PHY_ADR2  | O/LI/PD  | RGMII Receiver Control signal.                                                                                                                                  |  |

| 20                 | KA_CIL/IIII_ADK2 | U/LI/I D | PHY Address[2]                                                                                                                                                  |  |

| 27                 | RX_CLK/PHY_ADR1  | O/LI/PD  | RGMII Receiver Reference Clock. 125Mhz, 25MHz, or 2.5MHz                                                                                                        |  |

| 21                 | KA_CERTIT_ADRI   | O/LI/TD  | PHY Address [1]                                                                                                                                                 |  |

| LED                | 1                |          |                                                                                                                                                                 |  |

|                    |                  |          | LED0                                                                                                                                                            |  |

| 32                 | LED0/ENLDO       | O/LI/PU  | Light = Link up at 10Mbps                                                                                                                                       |  |

|                    |                  | 0,21,10  | Blinking = Transiting or Receiving                                                                                                                              |  |

|                    |                  |          | Enable LDO                                                                                                                                                      |  |

|                    |                  |          | LED1                                                                                                                                                            |  |

| 33                 | LED1/VOL_CFG0    | O/LI/PU  | Light = Link up at 100Mbps                                                                                                                                      |  |

|                    |                  |          | Blinking = Transiting or Receiving                                                                                                                              |  |

|                    |                  |          | RGMII Voltage Configure[0]                                                                                                                                      |  |

|                    |                  |          | LED2                                                                                                                                                            |  |

| 34                 | LED2/VOL_CFG1    | O/LI/PD  | Light = Link up at 1000Mbps                                                                                                                                     |  |

|                    |                  |          | Blinking = Transiting or Receiving                                                                                                                              |  |

TEL:0086-0769-88010888 https://www.dptel.com/

Songshan Lake · Dongguan · Guangdong

| RGMII Voltage Configure[1] |       |   |                                                                                   |  |

|----------------------------|-------|---|-----------------------------------------------------------------------------------|--|

| Others                     |       |   |                                                                                   |  |

| 39                         | Rbias | 0 | Bias Resistor Connection. External 2.49 k $\Omega$ 1% resistor connection to GND. |  |

### 2 Electrical Characteristics

# 2.1 Absolute Maximum Ratings

| Demonstern           | Sh al                | Value |      |      | TT-+*4 | Nutur |

|----------------------|----------------------|-------|------|------|--------|-------|

| Parameter            | Symbol               | Min.  | Тур. | Max. | Unit   | Notes |

|                      | $V_{DD_3V3}$         | -0.5  |      | 3.63 | V      |       |

|                      | V <sub>DDA_3V3</sub> | -0.5  |      | 5.05 | ×      |       |

| Power Supply Voltage | $V_{DD_1V}$          | -0.3  |      | 1.32 | v      |       |

|                      | V <sub>DDA_1V</sub>  |       |      | 1.32 |        |       |

|                      | $V_{DD\_IO}$         | -0.5  |      | 3.63 | V      |       |

| Storage temperature  | T <sub>STG</sub>     |       |      | 150  | °C     |       |

| Operating Junction   | TJun                 | 40    |      | 125  | °C     |       |

| Temperature          | I Jun                | -40   |      | 125  | C      |       |

| Lead Soldering       |                      |       |      | 260  | °C     |       |

| Temperature          |                      |       |      | 200  | U      |       |

# 2.2 Recommended Operating Conditions

| Table3. | Recommended | Operating | Conditions |

|---------|-------------|-----------|------------|

|---------|-------------|-----------|------------|

| Demonster                    | Ch al                                       |      | Value |      | Unit | Notes  |

|------------------------------|---------------------------------------------|------|-------|------|------|--------|

| Parameter                    | Symbol                                      | Min. | Тур.  | Max. | Unit | INOLES |

| 3.3V Power Supply<br>Voltage | V <sub>DD_3V3</sub><br>V <sub>DDA_3V3</sub> | 2.97 | 3.3   | 3.63 | V    |        |

| 1.0V Power Supply            | $V_{DD\_1V}$                                | 1.05 | 1.10  | 1.30 | V    |        |

| Voltage                      | V <sub>DDA_1V</sub>                         | 1.05 | 1.10  | 1.30 | V    |        |

| 3.3V Power Supply<br>Voltage | V <sub>DD_IO</sub>                          | 2.97 | 3.3   | 3.63 | V    |        |

| 2.5V Power Supply<br>Voltage | V <sub>DD_IO</sub>                          | 2.25 | 2.5   | 2.75 | V    |        |

| 1.8V Power Supply<br>Voltage | V <sub>DD_IO</sub>                          | 1.62 | 1.8   | 1.98 | V    |        |

| Max. Junction                | T <sub>JUNC</sub>                           | 0    |       | 125  | °C   |        |

Songshan Lake • Dongguan • Guangdong

| Demonstern                                   | 6h1                 |      | Value |      | U:4  | Neter                             |  |

|----------------------------------------------|---------------------|------|-------|------|------|-----------------------------------|--|

| Parameter                                    | Symbol              | Min. | Тур.  | Max. | Unit | Notes                             |  |

| Temperature                                  |                     |      |       |      |      |                                   |  |

| Operation temperature                        | Topr                | 0    | 25    | 70   | °C   |                                   |  |

| Thermal resistance -<br>junction to ambient  | $\theta_{JA}$       |      | 32    |      | °C/W | JEDEC with no air flow<br>TA=25°C |  |

| Thermal resistance -<br>junction to board    | $\theta_{JB}$       |      | 12    |      | °C/W | JEDEC with no air flow            |  |

| Thermal resistance -<br>junction to top case | θ <sub>JC-Top</sub> |      | 27    |      | °C/W | JEDEC with no air flow            |  |

# 2.3 DC Characteristics

| Demonstern                   | Sh al                       |      | Value |      | Unit | Natar                                           |  |  |

|------------------------------|-----------------------------|------|-------|------|------|-------------------------------------------------|--|--|

| Parameter                    | Symbol                      | Min. | Тур.  | Max. | Unit | Notes                                           |  |  |

|                              | $\mathbf{V}_{\mathrm{IH1}}$ | 2.0  |       |      | v    | V <sub>DDIO</sub> =3.3V                         |  |  |

| High-level input<br>voltage  | V <sub>IH2</sub>            | 1.7  |       |      | v    | V <sub>DDIO</sub> =2.5V                         |  |  |

|                              | $V_{\rm IH3}$               | 1.2  |       |      | v    | V <sub>DDIO</sub> =1.8V                         |  |  |

|                              | $V_{IL1}$                   |      |       | 0.8  | v    | V <sub>DDIO</sub> =3.3V                         |  |  |

| Low-level input<br>voltage   | V <sub>IL2</sub>            |      |       | 0.7  | V    | V <sub>DDIO</sub> =2.5V                         |  |  |

|                              | V <sub>IL3</sub>            |      |       | 0.5  | V    | V <sub>DDIO</sub> =1.8V                         |  |  |

|                              | Voh1                        | 2.4  |       | 3.6  |      | V <sub>DDI0</sub> =3.3V, I <sub>OH</sub> =-20mA |  |  |

| High-level output<br>voltage | Voh2                        | 2.0  |       | 2.8  | v    | V <sub>DDI0</sub> =2.5V, I <sub>OH</sub> =-20mA |  |  |

|                              | Vонз                        | 1.62 |       | 2.1  |      | V <sub>DDIO</sub> =1.8V, I <sub>OH</sub> =-10mA |  |  |

|                              | V <sub>OL1</sub>            | -0.3 |       | 0.4  |      | V <sub>DDI0</sub> =3.3V, I <sub>OH</sub> =20mA  |  |  |

| Low-level output<br>voltage  | V <sub>OL2</sub>            | -0.3 |       | 0.4  | V    | V <sub>DDI0</sub> =2.5V, I <sub>OH</sub> =20mA  |  |  |

|                              | Vol3                        | -0.3 |       | 0.4  |      | V <sub>DDIO</sub> =1.8V, I <sub>OH</sub> =10mA  |  |  |

#### Table4. DC Characteristics

# 2.4 Clock Characteristics

Table5.Clock Characteristics

Songshan Lake · Dongguan · Guangdong

|                      |                                | Min. | Тур. | Max. |     |

|----------------------|--------------------------------|------|------|------|-----|

| Crystal              |                                |      |      |      |     |

| Frequency            | $F_{XIN}\!/_{XOUT}$            |      | 25   |      | MHz |

| Stability            | $\Delta \mathbf{f}/\mathbf{f}$ | -50  |      | 50   | ppm |

| Oscillator Character | istics                         |      |      |      |     |

| Frequency            | F <sub>XIN</sub>               |      | 25   |      | MHz |

| Input High Voltage   | V <sub>XINH</sub>              | 2.0  |      |      | V   |

| Input Low Voltage    | V <sub>XINL</sub>              |      |      | 0.8  | V   |

| DutyCycle            | Duty_Cycle                     | 40   |      | 60   | %   |

| Stability            | $\Delta f/f$                   | -50  |      | 50   | ppm |

# 2.5 Timing Characteristics

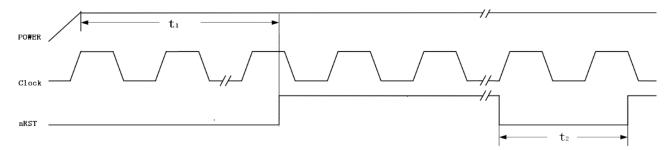

# 2.5.1Reset Timing

| Table6. | Reset Timing |

|---------|--------------|

|---------|--------------|

| Devemeter                                   | Symbol         |      | Unit |      |      |

|---------------------------------------------|----------------|------|------|------|------|

| Parameter                                   | Symbol         | Min. | Тур. | Max. | Unit |

| Reset de-assert time after power on         | t1             | 10   |      |      | ms   |

| Minimum reset pulse during normal operation | t <sub>2</sub> | 10   |      |      | ms   |

Songshan Lake · Dongguan · Guangdong

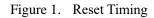

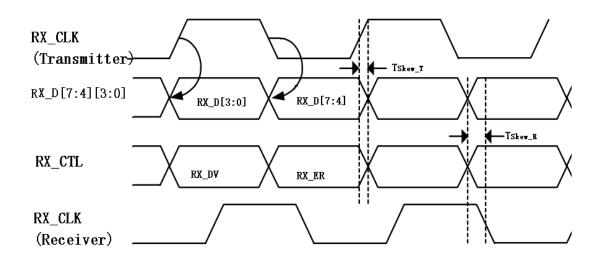

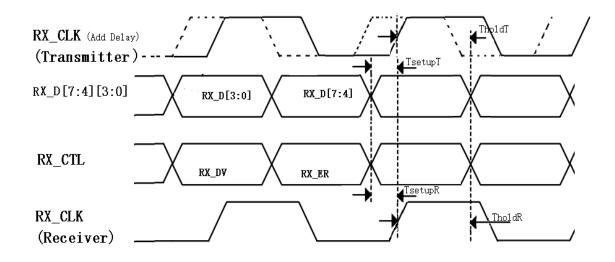

# 2.5.2 RGMII Interface Timing

Figure 2. RGMII Transmit Timing

Songshan Lake · Dongguan · Guangdong

Table7. RGMII Timing

| Parameter                                  | Symbol              | Value |      |      | Unit | Notes      |

|--------------------------------------------|---------------------|-------|------|------|------|------------|

| rarameter                                  | Symbol              | Min.  | Тур. | Max. | Unit | Inotes     |

| Clock Cycle Duration                       | T <sub>Cycle</sub>  | 7.2   | 8.0  | 8.8  | ns   |            |

|                                            |                     | 45    | 50   | 55   | %    | 1000Base-T |

| Duty Cycle                                 | Duty                | 40    | 50   | 60   | %    | 100Base-TX |

|                                            |                     | 40    |      |      |      | 10Base-Te  |

| Rise/Fall Time                             | $T_{Rise}/T_{Fall}$ |       |      | 0.75 | ns   | 20~80%     |

| Data to Clock output Skew (at receiver)    | T <sub>Skew_R</sub> | 1     |      |      | ns   |            |

| Data to Clock output Skew (at transmitter) | $T_{Skew\_T}$       | -0.5  |      | 0.5  | ns   |            |

Songshan Lake · Dongguan · Guangdong

| Parameter                                                                                | Symbol  | Value |      |      | Unit | Natar |

|------------------------------------------------------------------------------------------|---------|-------|------|------|------|-------|

| Farameter                                                                                | Symbol  | Min.  | Тур. | Max. | Unit | Notes |

| Data to Clock Output Setup Time at transmitter<br>(with delay integrated at transmitter) | TsetupT | 1.0   | 2.0  |      | ns   |       |

| Clock to Data Output Hold Time at transmitter<br>(with delay integrated at transmitter)  | TholdT  | 1.0   | 2.0  |      | ns   |       |

| Data to Clock Input Setup Time at receiver<br>(with delay integrated at transmitter)     | TsetupR | 1.0   | 2.0  |      | ns   |       |

| Clock to Data Input Hold Time at receiver<br>(with delay integrated at transmitter)      | TholdR  | 1.0   | 2.0  |      | ns   |       |

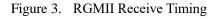

# 2.5.3 SMI Interface Timing

| Table8. | RGMII | Timing |

|---------|-------|--------|

|---------|-------|--------|

| Parameter                       | Symbol | Value |      |      | Unit | Notes  |

|---------------------------------|--------|-------|------|------|------|--------|

| rarameter                       | Symbol | Min.  | Тур. | Max. | Umt  | Inotes |

| MDC Clock Cycle Duration        | T1     | 80    |      |      | ns   |        |

| MDC Clock High Level Duration   | T2     | 32    |      |      |      |        |

| MDC Clock Low Level Duration    | Т3     | 32    |      |      |      |        |

| MDC to MDIO (output) delay time | T4     |       |      | 20   |      |        |

| MDIO (input) to MDC setup time  | T5     | 10    |      |      |      |        |

| MDIO (input) to MDC hold time   | T6     | 10    |      |      |      |        |

Songshan Lake · Dongguan · Guangdong

### 3 Detail Description

### 3.1 Block Diagram

Figure 5. Block Diagram

# 3.2 Feature Description

### 3.2.1 WoL (Wake-on-LAN)

Wake-on-LAN provides a mechanism to detect dedicated frames and inform the connected MAC through either a register status change, WoL indication, or an interrupt flag. The connected devices (MAC) placed above the Physical Layer to operate in a low power mode until special magic packet are detected.

### 3.2.1.1 Magic Packet

If register field WOL\_CON bit3 is set to "1", Magic Packet Event is enabled. Magic Packet is defined as 6 bytes of "FF" followed by 16 iterations of the destination address, which is the waked up MAC address that is defined in register field WOL\_MAC\_ADDH, WOL\_MAC\_ADDM, WOL\_MAC\_ADDL. A "1" in register INTSR bit 6 indicates there is a Magic Packet received and it would be cleared after read.

# 3.2.2 IEEE 802.3az-2010 (EEE)

The DAP8211R supports IEEE 802.3az-2010(EEE: Energy Efficient Ethernet). EEE defines a negotiation method to enable link partners to decide whether EEE is supported.

Based on link utilization efficiency and EEE protocol, the transitions would work in different mode. When no packets are being transmitted, DAP8211R would work in Low Power Idle mode to save power. As soon as packets to be transmitted, DAP8211R returns to normal mode, and this doesn't impact the link status and dropping frames.

### 3.2.3 SyncE

DAP8211R supports Sync-E function.

When this function is enabled in slave mode, recovered 25MHz/125MHz clock will be output through CLK<sub>OUT</sub> pad.

If the device is in master mode, the CLK<sub>OUT</sub> will output the clock based on the local free run PLL.

### 3.2.4 nINT/nPME

The nINT/nPME pin (pin 31) is designed to notify both interrupt and WoL events. It is nINT mode at default. It could generate interrupts to external SOC.

DAP8211R provides an active low interrupt output based on change of the PHY status. Every interrupt condition is represented by the read-only general interrupt status register (Interrupt Status Register (Basic register 0x13)).

The interrupts can be individually enable or disable by setting or clearing bits in the interrupt enable register (Interrupt Mask Register (Basic register 0x12)).

If nPME mode is selected (Ext\_0xa00a, bit[6]=1), pin 31 becomes a fully functional nPME pin. Note that the interrupt function is disabled in this mode.

The behavior of nINT is level-triggered, the behavior of nPME is level-triggered or pulse-triggered which is controled by EXT 0xA00A bit[0].

### 3.2.5 MDI Interface

DAP8211R supports the 1000Base-T, 100Base-TX and 10Base-Te standard as defined by the IEEE 802.3, 802.3ab and 802.3u standards.

In 1000Base-T mode, the PHY will use four pairs MDI channels for communication at 125MBaud/s through D/A or A/D converter. The communicated data are encoded/decoded in 4D-PAM5 and RGMII works at a clock speed of 125MHz. For transmitter, pulse shaping and slew rate control technology are used to eliminate EMI problem. A hybrid analog front end is employed to reduce near-end echo, which allows transmitter and receiver to share one transformer. In the digital domain, echo cancellation, cross-talk cancellation, baseline drift cancellation and adaptive equalization are realized

In 100Base-TX mode, the PHY will use two pairs MDI channels (Pairs A and B) for communication. The communicated data are encoded/decoded in 4B/5B and RGMII works at a clock speed of 25MHz.

In 10Base-Te mode, the PHY will also use two MDI channels (Pairs A and B) for communication. The communicated data are encoded/decoded in Manchester and RGMII works at a clock speed of 2.5MHz.

# 3.2.6 MAC Interface(RGMII)

The DAP8211R supports RGMII 2.0 interface between MAC and PHY. The RGMII(Reduced Gigabit Media Independent Interface) is designed to reduce the number of pins required to interconnect the MAC and PHY (12 pins for RGMII). There are 6 pins for transmit path and 6 pins for receive path. For 100M/10M application, RGMII is similar to MII. The only difference is that tx\_er/rx\_er is transmitted by TX\_CTL/RX\_CTL on the falling edge of clock. Both rising and falling edges of the clock are used. For 1000M, the GTX\_CLK and RX\_CLK clocks are 125 MHz, and for 10 M and 100 M, the clock frequencies are 2.5 MHz and 25 MHz respectively.

### 3.2.7 Management Interface

The management interface provides access to the internal registers through the MDC and MDIO pins. The MDC signal is the management data clock reference to the MDIO signal, and clock rates up to 12.5MHz. The MDIO is the management data input/output and is a bi-directional signal that runs synchronously to MDC. The MDIO pin needs a pull-up resistor.

# 3.2.8 Loopback Mode

There are several options for loopback mode that test and verify various functional blocks within the PHY. Enabling loopback mode allows in-circuit testing of the digital and analog data paths. Generally, the DAP8211R may be configured to 4 loopback modes.

| Loopback Mode     | Description                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCS Loopback      | When BMCR register field Loopback is set to "1", data sent through RGMII will route to PCS layer rx port through PCS TX path. Then these data will route back to RGMII RX pad through PCS RX path.                               |

| External Loopback | An external loopback stub allows testing the complete data path without the need of a link partner. In this case it seems the data send through RGMII TX interface with be forwarded to RGMII RX interface through MDI interface |

| Remote Loopback   | When MISC_CON register field Remote_loopback is set to "1", data transmitted from rgmii tx interface will route back to rgmii rx interface. This checks if rgmii works correctly for remote link.                                |

# 3.2.9 Hardware Configuration

The RGMII I/O pad voltage, RGMII TX/RX clock delay, and PHY address can be set by hardware. These configurations are setup through dedicated IO pin with external pullup/pulldown resistor. When power on reset is de-asserted, the hardware circuit will sample values on these dedicated IO pin.

Songshan Lake · Dongguan · Guangdong

| Part Number | Dedicated IO      | Desc                                                                                                                                                                                                                    | ription                                                                                                                                                                                  |                       |              |  |  |  |  |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--|--|--|--|

| DAP8211R    | ADR[2:0]          | to 0x                                                                                                                                                                                                                   | Set the PHY address for the device. It supports the PHY address from $0x0$ to $0x7$ . The $0x0$ is a broadcast address on default. This function can be disabled by setting MDIO config. |                       |              |  |  |  |  |

|             | RXDLY             | 1: add                                                                                                                                                                                                                  | RGMII rx clock delay setting.<br>1: add 2ns delay on RX_CLK when RX_CLK is 125MHz<br>add 8ns delay on RX_CLK when RX_CLK is 25MHz/2.5MHz,<br>0: no delay                                 |                       |              |  |  |  |  |

|             | TXDLY             | 1: ad                                                                                                                                                                                                                   | RGMII tx clock delay setting.<br>1: add 2ns to TX_CLK<br>0: no delay                                                                                                                     |                       |              |  |  |  |  |

|             | PLLOFF            | In sleep mode, PLL off configuration.                                                                                                                                                                                   |                                                                                                                                                                                          |                       |              |  |  |  |  |

|             | EN <sub>ldo</sub> | <ul> <li>Control of internal LDO for IO supply:</li> <li>1: disable internal LDO, external power supply is for IO.</li> <li>0: enable internal LDO.</li> <li>IO supply is determined by strap VOL_CFG [1:0].</li> </ul> |                                                                                                                                                                                          |                       |              |  |  |  |  |

|             | VOL_CFG[1:0]      | RGMII I/O Voltage selection:                                                                                                                                                                                            |                                                                                                                                                                                          |                       |              |  |  |  |  |

|             |                   |                                                                                                                                                                                                                         | VOL_CFG[1:0]                                                                                                                                                                             | External Power Supply | Internal LDO |  |  |  |  |

|             |                   |                                                                                                                                                                                                                         | 00                                                                                                                                                                                       | NA                    | 3.3V         |  |  |  |  |

|             |                   |                                                                                                                                                                                                                         | 01                                                                                                                                                                                       | 2.5V                  | 2.5V         |  |  |  |  |

|             |                   |                                                                                                                                                                                                                         | 10                                                                                                                                                                                       | 1.8V                  | 1.8V         |  |  |  |  |

|             |                   |                                                                                                                                                                                                                         | 11                                                                                                                                                                                       | 1.8V                  | 1.8V         |  |  |  |  |

### 3.2.10 Auto-Negotiation

DAP8211R supports Auto-Negotiation function which is defined in 802.3. Auto negotiation is enabled by default and can be disabled by register configuration.

Auto negotiation supports choosing the operation mode automatically by comparing its own abilities and link partner abilities. The advertised abilities include:

TEL:0086-0769-88010888 ht

https://www.dptel.com/

- Speed: 10/100/1000Mbps

- Duplex mode: full duplex/ half duplex

Auto negotiation is initialized when the following scenarios happen:

- Power-up/Hardware/Software reset

- Auto negotiation restart

- Transition from power down to power up

- Link down

#### 3.2.11 Crossover Detection and Auto-Correction

The function implements crossover detection automatically for MDI/MDIX cables which easies connection process. The DAP8211R also implements polarity auto correction when cable happens to have wrong polarity connected.

#### 3.2.12 Baseline Wander Correction

DAP8211R uses an advanced baseline wander cancellation circuit that continuously monitors and compensates for this effect, minimizing the impact of DC baseline shift on the overall error rate. Baseline wander is due to the AC coupling of the Ethernet link to the transceiver and the inability of the AC coupling to maintain voltage levels over short periods of time. As a result, the transmitted pulse is distorted, resulting in an incorrect sampling value for the affected pulse. Baseline wander is more problematic in 1000Base-T environments than in 100Base-TX environments due to DC baseline drift in transmitted and received signals.

#### 3.2.13 Echo Cancellation

DAP8211R supports echo cancellation. A hybrid circuit is used to transmit and receive simultaneously on each pair. A signal reflects back as an echo if the transmitter is not perfectly matched to the line. Other connector or cable imperfections, such as patch panel discontinuity and variations in cable impedance along the twisted pair cable, also result in drastic SNR degradation on the receive signal. The device implements a digital echo canceller to adjust for echo and is adaptive to compensate for the varied channel conditions.

### 3.2.14 Crosstalk Cancellation

DAP8211R supports crosstalk cancellation.

The 1000Base-T physical layer uses all four pairs of wires to transmit data. Because four twisted pair pairs are tied together, significant high-frequency crosstalk occurs between the tied adjacent pairs. The device uses three parallel crosstalk cancellers on each receiving channel to eliminate the crosstalk. DAP8211R eliminates the crosstalk by subtracting estimates of these signals from the equalizer output.

# 3.2.15 LED Configuration

DAP8211R has three LED outputs for indicator.

The LEDs can be programmed to different status functions from their default value. The LED interface can either be controlled by the PHY or controlled manually, independent of the state of the PHY. They can be used to indicate operation speed, duplex mode, and link status. The LEDs can be programmed to different status functions from their default value. They can also be controlled directly from the register interface.

Because the LED pins are duplexed with the hardware configure dedicated pins, the external circuit required for hardware configure and LED circuit must be considered in order to avoid confliction.

### 3.2.16 Clock

DAP8211R can use crystal or oscillator as clock reference input.

If use oscillator or other clock sources, use  $X_{IN/OUT}$  as clock input pin, and another pin should be left floating or ground.

### 3.2.17 Sleep Mode

DAP8211R (D) will enter sleep mode when UTP port link down and no signals over UTP cable for 40 seconds.

In sleep mode, DAP8211R (D) will disable almost all the circuits except crystal clock, 10BASE-Te and MDC/MDIO interface.

In sleep mode, at regular intervals, DAP8211R (D) will wake up and transmit signals via TRXP1/TRXN1. The time interval is a random value of about 2.7s.

DAP8211R (D) exits sleep mode once it detects a UTP line signal

# 3.2.18 Power Supply

DAP8211R integrates the internal switching regulator or linear regulator that regulates 3.3V power source to 1.1V power output for core power.

DAP8211R with switching regulator is preferred with lower power dissipation.

DAP8211R implements an option for the RGMII power pins and supports 3.3/2.5/1.8V IO voltage. For DAP8211R, RGMII power could be supplied from an internal regulator(2.5/1.8V) or from an external power source(3.3/2.5/1.8V).

### 3.2.19 Reset

The DAP8211R can be reset by a hardware or software reset.

The DAP8211R has a nRST pin to reset the chip. For a complete PHY reset, this pin must be asserted low for at least 10ms for the internal regulator. All registers will return to default values after a hardware reset. After nRST is released, DAP8211R latches input value on strapping pins which are used as configuration information to provide flexibility in application.

IEEE registers software reset is accomplished by setting the reset bit (bit 15) of the BMCR register (address 0x0000). This bit resets the IEEE-defined standard registers.

### 4 Registers

|   | Register Group          | Description                       |  |  |

|---|-------------------------|-----------------------------------|--|--|

| 1 | Basic Register          | Basic Register based on IEEE802.3 |  |  |

| 2 | Package Generation      | The Package Generation register   |  |  |

|   | Extended Register       | based on Extended register        |  |  |

|   |                         | mapping                           |  |  |

| 3 | General Extend Register | General Extend Register based on  |  |  |

|   |                         | Extended Register Mapping         |  |  |

| 4 | MMD Register            | Extend Register based on MMD      |  |  |

|   |                         | Register Mapping                  |  |  |

The DAP8211R includes 3 register groups.

#### Register Access Types